### **VLSI COMPANIES IN INDIA**

- <u>Motorola India</u> IC design center

- <u>Texas Instruments</u> IC design center in Bangalore

- <u>VLSI India</u> ASIC design and FPGA services

- <u>VLSI Software</u> Design of electronic design automation tools

- <u>Microchip Technology</u> Offers VLSI CMOS semiconductor components for embedded systems

- <u>Delsoft</u> Electronic design automation, digital video technology and VLSI design services

- <u>Horizon Semiconductors</u> ASIC, VLSI and IC design training

- <u>Bit Mapper</u> Design, development & training

- <u>Calorex Institute of Technology</u> Courses in VLSI chip design, DSP and Verilog HDL

- <u>ControlNet India</u> VLSI design, network monitoring products and services

- <u>E Infochips</u> ASIC chip design, embedded systems and software development

- <u>EDAIndia</u> Resource on VLSI design centres and tutorials

- <u>Cypress Semiconductor</u> US semiconductor major Cypress has set up a VLSI development center in Bangalore

- <u>VDAT 2000</u> Info on VLSI design and test workshops

### **VLSI COMPANIES IN INDIA**

- <u>Sandeepani</u> VLSI design training courses

- <u>Sanyo LSI Technology</u> Semiconductor design centre of Sanyo Electronics

- <u>Semiconductor Complex</u> Manufacturer of microelectronics equipment like VLSIs & VLSI based systems & sub systems

- <u>Sequence Design</u> Provider of electronic design automation tools

- <u>Trident Techlabs</u> Power systems analysis software and electrical machine design services

- <u>VEDA IIT</u> Offers courses & training in VLSI design & development

- <u>Zensonet Technologies</u> VLSI IC design firm <u>eg3.com</u> Useful links for the design engineer

- <u>Analog Devices India Product Development Center</u> Designs DSPs in Bangalore

- <u>CG-CoreEl Programmable Solutions</u> Design services in telecommunications, networking and DSP

# Physical Design, CAD Tools.

- SiCore Systems Pvt. Ltd. 161, Greams Road, ...

- Silicon Automation Systems (India) Pvt. Ltd. (SASI) ...

- Tata Elxsi Ltd. VLSI Design Group, ...

- Tata Infotech Ltd. Bangalore. ...

- Texas Instruments (India) Ltd. Golf View Homes, ...

- TranSwitch (India) Pvt. Ltd. ...

- Vedatech India (Software) Pvt. Ltd.

### 14EC770 : ASIC DESIGN

### • Preamble

- 14EC270 : Digital Logic Circuit Design

- 14EC520 : Digital CMOS Systems

### Objective

This course provide the students, the knowledge about

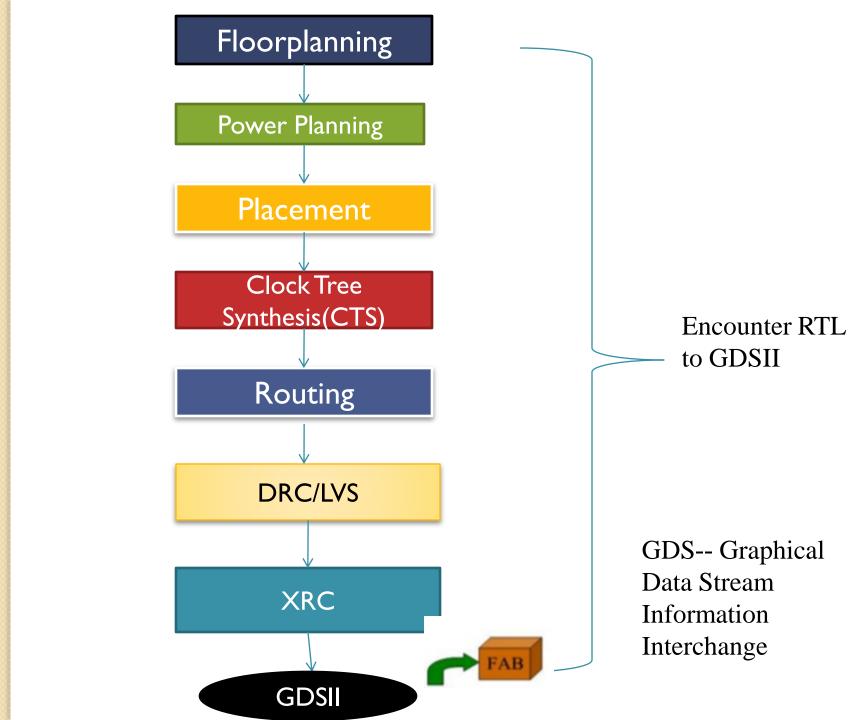

- Physical design flow of IC

- Floor-planning, Placement and Routing

- Experiments explore complete digital design flow of programmable ASIC through VLSI EDA tools.

- Students work from design entry using verilog code to GDSII file generation of an ASIC.

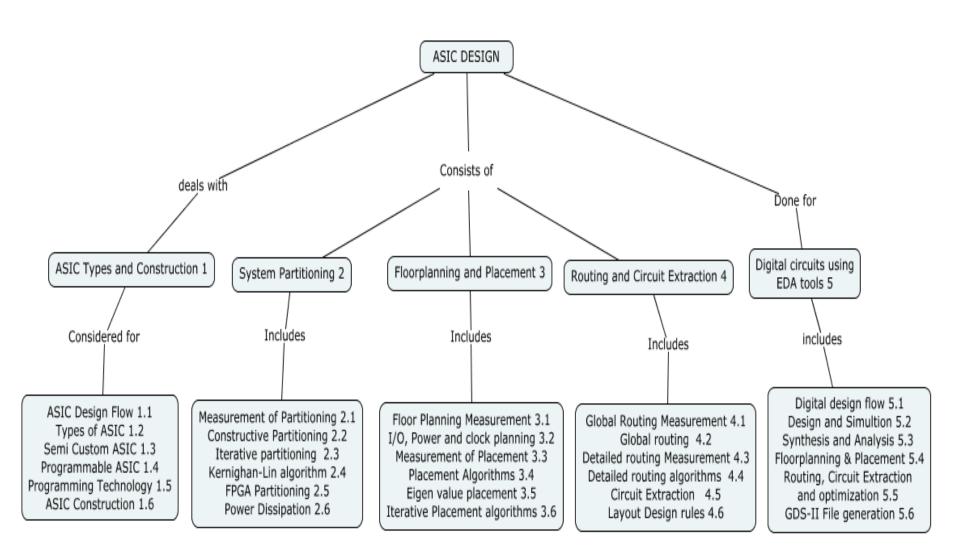

# Concept MAP

### **Course Outcomes**

| C01 | Describe the design flow, types and the programming technologies of an ASIC and its construction.                                                                                                                                                                                                                            | Understand   |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| C02 | Describe the goals, objectives, measurements and algorithms of partitioning then apply those algorithms to partition the network to meet the objectives.                                                                                                                                                                     | Apply        |

| C03 | Describe the goals, objectives, measurements and<br>algorithms of floorplanning & placement then apply those<br>algorithms to place the logic cells inside the flexible blocks<br>of an ASIC to meet the objectives.                                                                                                         | Apply        |

| CO4 | Describe the goals, objectives, measurements and<br>algorithms of routing then apply those algorithms to route<br>the channels then describing various circuit extraction<br>formats and Investigate the issues and discover solutions in<br>each step of physical design flow of an ASIC.                                   | Analyze      |

| C05 | Design an ASIC for digital circuits with ASIC design flow<br>steps consists of simulation, synthesis, floorplanning,<br>placement, routing, circuit extraction and generate GDSII<br>File for fabrication of an ASIC, then analyze the ASIC to<br>meet the performance in terms of area, speed and power<br>using EDA tools. | Analyze<br>7 |

# **Assessment Pattern**

| Bloom's    | Contir | Terminal |           |             |

|------------|--------|----------|-----------|-------------|

| Category   | 1      | 2        | 3         | Examination |

| Remember   | 20     | 0        | Practical | 0           |

| Understand | 50     | 20       |           | 20          |

| Apply      | 30     | 30       |           | 30          |

| Analyse    | 0      | 50       |           | 50          |

| Evaluate   | 0      | 0        | 1         | 0           |

| Create     | 0      | 0        |           | 0           |

# **Integrated Circuit**

Wafer :

**\*** Wafer Lot:

✤ Die:

A circular piece of pure silicon (10-15 cm in dia, wafers of 30 cm dia are expected soon)

5 ~ 30 wafers, each containing hundreds of chips(dies) depending upon size of the die A rectangular piece of silicon that contains one IC design

Mask Layers: Each IC is manufactured with successive mask layers(10 – 15 layers)

First half-dozen or so layers define transistors

Other half-dozen define Interconnect

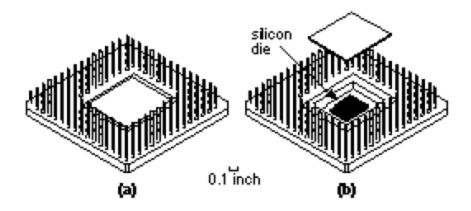

# Integrated Circuit (IC) in a package

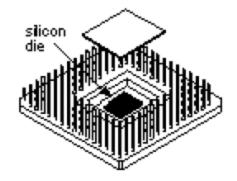

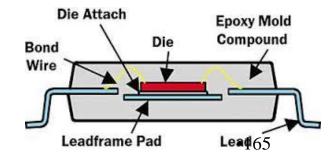

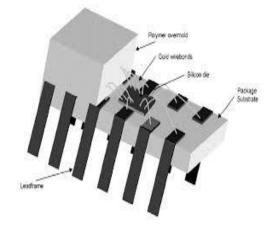

(a) A pin-grid array (PGA) package.

(b) The silicon die or chip is under the package lid.

# Evolution of IC

- SSI (Small-Scale Integration)-(1962)

- Tens of Transistors

- NAND, NOR

- MSI (Medium-Scale Integration)-(late 1960)

- Hundreds of Transistors

- Counters

- LSI (Large-Scale Integration)-(mid 1970)

- Tens of Thousands of Transistors

- First Microprocessor

- VLSI (Very Large-Scale Integration)-(1980)

- started Hundreds of Thousands of Transistors-several billion transistors in 2009

- 64 bit Microprocessor with cache memory and floating-point arithmetic units

- ULSI (Ultra Large-Scale Integration)-(late 1980)

- More than about one million circuit elements on a single chip.

- The Intel 486 and Pentium microprocessors, use ULSI technology

# IC technologies

- Bipolar

- More accuracy

- MOS

- Gate-Aluminium

- Low power consumption

- Low cost

- CMOS

- Gate-Poly-Silicon

- Low power consumption

- Low cost

- BiCMOS

# Types of IC

- Standard ICs

- Glue Logic-Microelectronic system design then becomes a matter of defining the functions that you can implement using standard ICs and then implementing the remaining logic functions (sometimes called glue logic ) with one or more custom ICs.

- ASIC

- ASSP (Application-Specific Standard Products)

### **ASIC and Non ASIC**

- Examples of **ICs that are** *not ASICs* include standard parts such as:

- *memory chips sold* as a commodity item—ROMs, DRAM, and SRAM; microprocessors;

- TTL or TTL-equivalent ICs at SSI, MSI, and LSI levels.

- Examples of **ICs that** *are* **ASICs** *include*:

- a chip for a toy bear that talks;

- *a chip for a* satellite;

- a chip designed to handle the interface between memory and a microprocessor for a workstation CPU;

- a chip containing a microprocessor as a cell together with other logic.

- **ASSP** (two ICs that might or might not be considered ASICs )

- controller chip for a PC and a chip for a modem.

- Both of these examples are specific to an application (shades of an ASIC) but are sold to many different system vendors (shades of a standard part).

ASICs such as these are sometimes called **application-specific standard**<sub>4</sub> **products ( ASSPs ).**

# Measurement of IC

- Gate Equivalent

- Number of gates or transistors

- Gate refer to two input NAND Gate

- In CMOS, each NAND gate consist of 4 transistors

- Example : 10k gate IC

- (10,000 two-input NAND gates or 40,000 transistors in CMOS)

- Feature Size (smallest feature size  $=\lambda$ )

- Half of smallest transistor length

- Example: 0.5µm IC

- Feature size,  $\lambda = 0.25 \mu m$

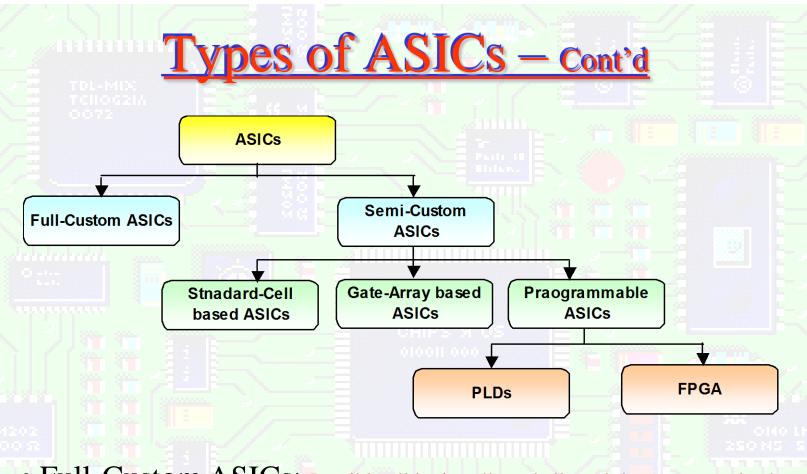

- Full-Custom ASICs: Possibly all logic cells and all mask layers customized

- Semi-Custom ASICs: all logic cells are pre-designed and some (possibly all) mask layers customized

### **□Full-Custom ASICs**

Include some (possibly all) customized logic cells

✤ Have all their mask layers customized

Manufacturing lead time is typically 8 weeks (time taken to make the IC does not include design time)

Full-custom ASIC design makes sense only

When no suitable existing libraries exist or

Existing library cells are not fast enough or

The available pre-designed/pre-tested cells consume too much power that a design can allow or

The available logic cells are not compact enough to fit or

$\checkmark$  ASIC technology is new or/and so special that no cell library exits. <sup>17</sup>

### **□Full-Custom ASICs**

Advantages:

Offer highest performance

lowest cost (smallest die size)

Disadvantages

Increased design time

Increased Complexity

Higher design cost

Higher risk.

### **Some Examples:**

- Microporcessor,

- High-Voltage Automobile Control Chips

- Ana-Digi Communication Chips

- Sensors and Actuators

### Semi-Custom ASICs

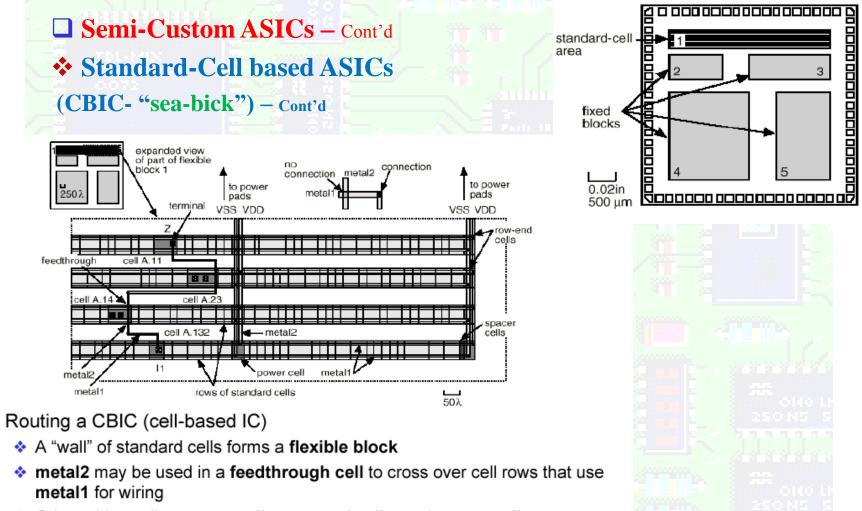

- Standard-Cell based ASICs (CBIC- "sea-bick")

- ✓ Use predesigned logic cells (Called standard cells) from

- ✓ standard cell libraries

- ✓ other mega-cells (Microcontroller or Microprocessors)

- ✓ full-custom blocks

- ✓ System-Level Macros(SLMs)

- ✓ Functional Standard Blocks (FSBs)

- ✓ cores etc

- ✓ Get all mask layers customized- transistors and interconnect

- ✓ Manufacturing lead time is about 8 weeks

- ✓ Custom blocks can be embedded

Other wiring cells: spacer cells, row-end cells, and power cells

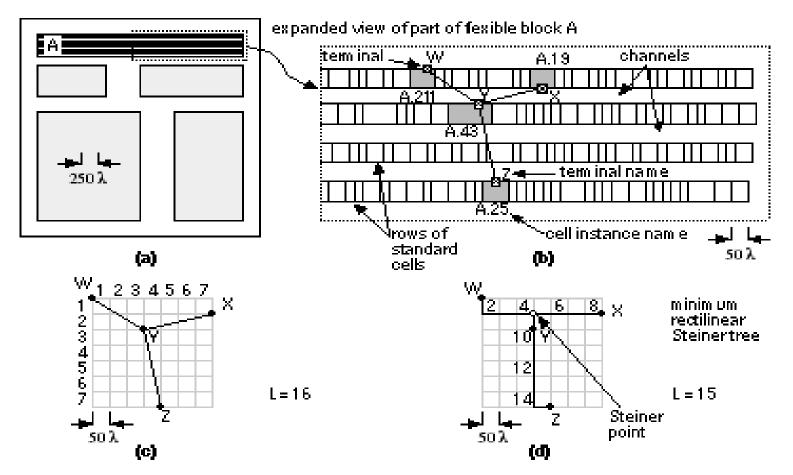

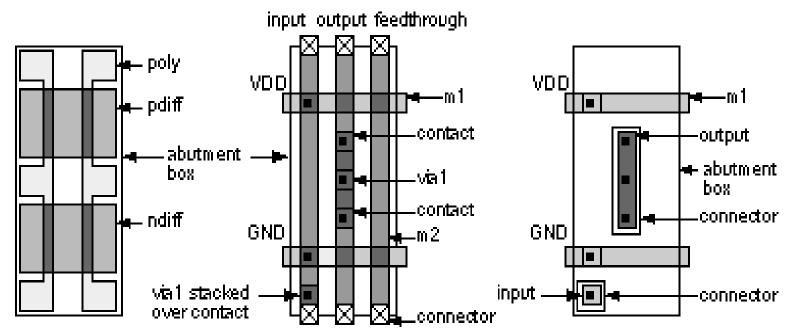

### **Standard Cell in Flexible block of CBIC**

- Std cell in library is constructed using full-custom design methodology-

- Same performance and flexibility but reduce time and risk.

- ASIC designer defines only placement of standard cells

- It can be placed anywhere on silicon.

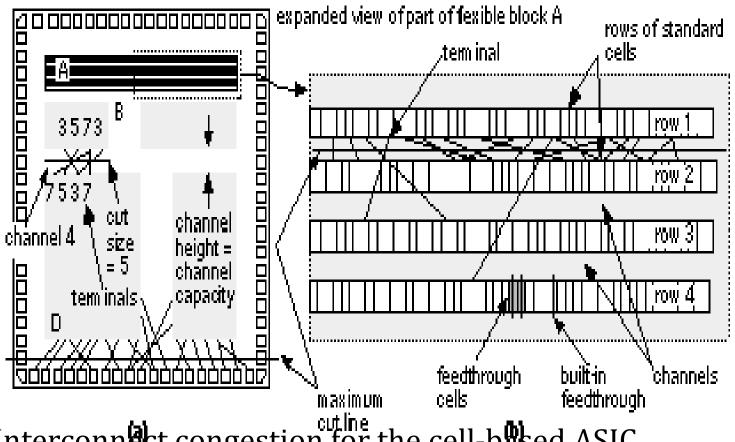

### **Construction of Flexible blocks in CBIC**

- Standard cells are designed like bricks in a wall.

- Groups of standard cells fit horizontally to form rows.

- The rows stack vertically to form flexible blocks- reshape during design

- Flexible blocks connected with other std cell blocks or full custom block

### <u>Types of ASICs – Cont'd</u>

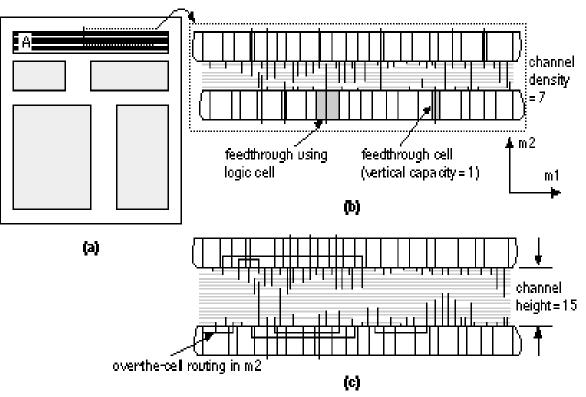

### □ Wiring cells in Standard Cell based ASICs

#### •Feedthrough cell:

•Piece of metal that is used to pass a signal through a cell or to a space in a cell waiting to be used as a feedthrough

#### •Spacer cells

•The width of each row of standard cells is adjusted so that they may be aligned using **spacer cells**.

#### •Row end cells

•The power buses, or rails, are then connected to additional vertical power rails using row-end cells at the aligned ends of each standard-cell block.

#### • Power cells

•If the rows of standard cells are long, then vertical power rails can also be run in metal2 through the cell rows using special **power cells that just connect** to VDD and GND.

•Usually the designer manually controls the number and width of the vertigal power rails connected to the standard-cell blocks during physical design.

### □ Advantages of CBIC

- Save time, money, reduce risk

- Standard cell optimized individually for speed or area

### **Disadvantages of CBIC:**

- Time to design standard cell library

- Expenses of designing std cell library

- Time needed to fabricate all layers of the ASIC for new design

#### Semi-Custom ASICs - Cont'd

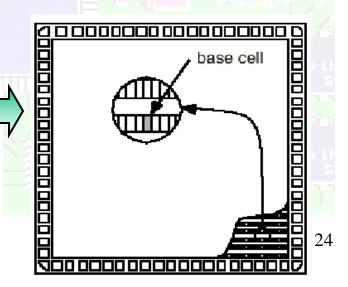

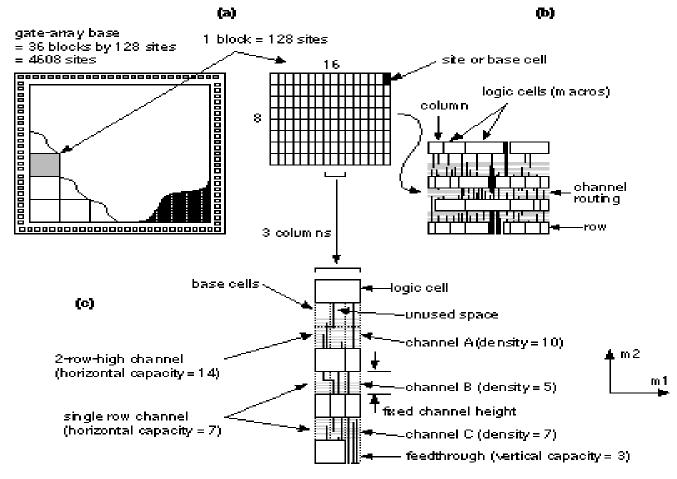

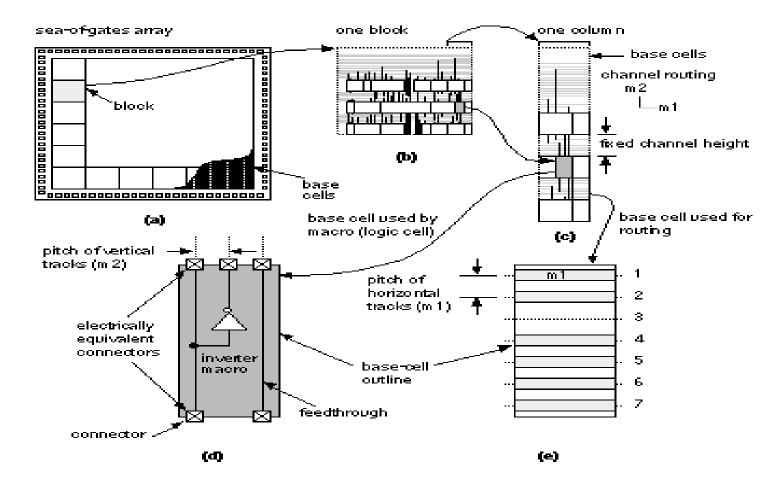

#### \* Gate Array based ASICs

- **Transistors are predefined** on the silicon wafer

- ✤Predefined pattern of transistors on a gate array is base array.

Smallest element repeated to form base array is **base cell.**

♦ Only the top few layers of metal, which define the interconnect between transistors, are defined by the designer using custom masks. It is often called a masked gate array (MGA).

Less turnaroundtime: fewdays or couple of weeks.

A gate array, masked gate array, MGA, or prediffused array uses macros (books) to reduce turnaround time and comprises a base array made from a base cell or primitive cell. There are three types:

- Channeled gate arrays

- Channelless gate arrays

- Structured gate arrays

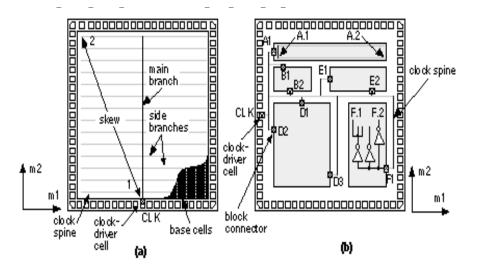

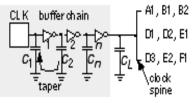

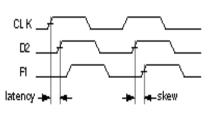

#### A channeled gate array

- Only the interconnect is customized

- The interconnect uses predefined spaces between rows of base cells

- Manufacturing lead time is between two days and two weeks

- ✤Similar to CBIC –but here space is fixed

### Semi-Custom ASICs – Cont'd

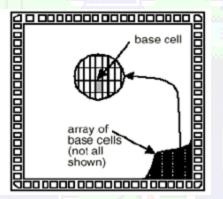

- Chanelless Gate Array ASIC

- A channelless gate array (channelfree gate array, sea-of-gates array, or SOG array)

- Only some (the top few) mask layers are customized — the interconnect

- Manufacturing lead time is between two days and two weeks.

•The key difference between a channelless gate array and channeled gate array

•there are **no predefined areas set aside for routing between cells on a channelless gate array**.

•Use an **area of transistors for routing in a channelless array**, we do not make any contacts to the devices lying underneath; we simply leave **the transistors unused**.

•The logic density—the amount of logic that can be implemented in a given silicon area is higher for channelless gate array

Semi-Custom ASICs – Cont'd Solution State Array ASIC

Solution Array ASIC •contact mask is customized in a channelless gate array, but is not usually customized in a channeled gate array. This leads to denser cells in the channelless architectures. •Customizing the contact layer in a channelless gate array allows us to increase the density of gate-array cells because

we can route over the top of unused contact sites.

### Semi-Custom ASICs – Cont'd

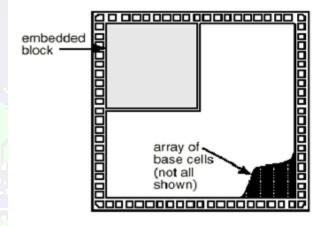

#### \* Structured Gate Array based ASICs

- An embedded gate array or structured gate array (masterslice or masterimage)

- Only the interconnect is customized

- Custom blocks (the same for each design) can be embedded

- Manufacturing lead time is between two days and two weeks.

•An embedded gate array or structured gate array (also known as masterslice or masterimage) combines some of the features of CBICs and MGAs.

•One of the **disadvantages of the MGA** is the **fixed gate-array base cell**. This makes the **implementation of memory, for example, difficult and inefficient.**

• In an embedded gate array we set aside some of the IC area and dedicate it to a specific function.

• This embedded area either can contain a different base cell that is more suitable for building memory cells, or it can contain a complete circuit block, such as a microcontroller.

### **Channelled gate array**

Adv: Specific space for interconnection

Disadv: compared to CBIC space is not adjustable

### **Channelless gate array**

Adv:

- Logic density is higher for channelless gate array

- Contact layers are customized

Disadv:

- No specific area for routing

- Rows of transistors used for routing are not used for other purpose.

### **Structured Gate Array**

Adv:

- Embedded gate array set in some of IC area and dedicate to specific function-customized.

- Increase area efficiency, performance of CBIC

- low cost and fast turn around of MGA

Disadv:

Embedded function is fixed

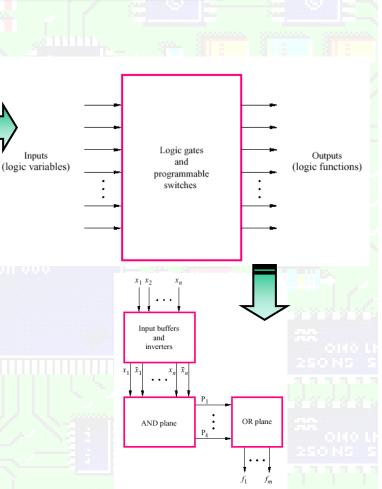

Inputs

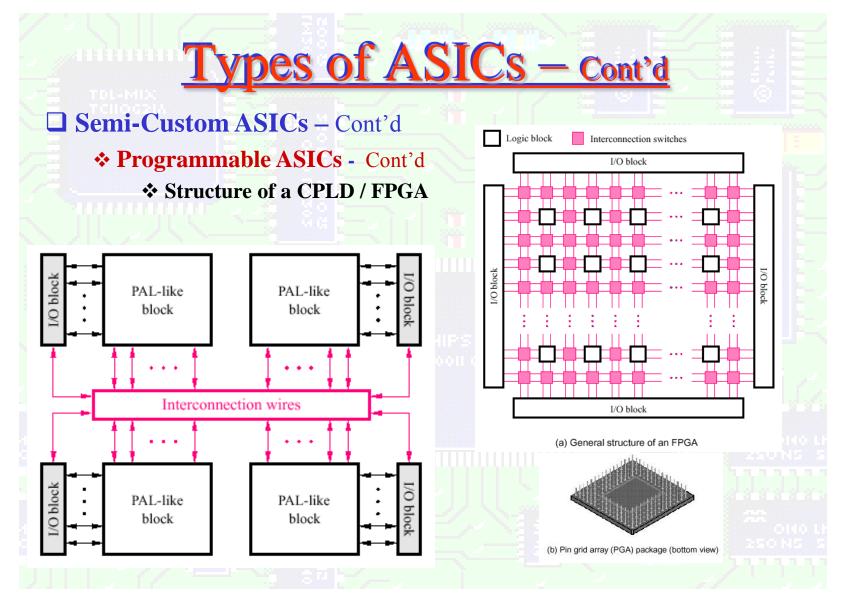

### □ Semi-Custom ASICs – Cont'd

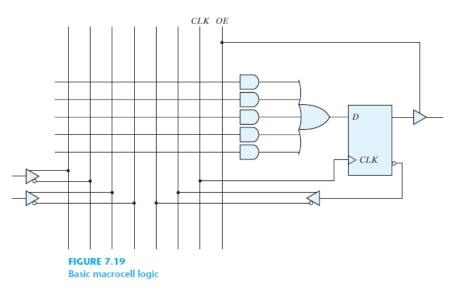

#### \* Programmable ASICs

✓ **PLDs** - PLDs are low-density devices which contain 1k - 10 k gates and are available both in bipolar and CMOS technologies [PLA, PAL or GAL]

#### ✓ CPLDs or FPLDs or FPGAs -

FPGAs combine architecture of gate arrays with programmability of PLDs.

#### ✓ User Configurable

✓ Contain Regular Structures circuit elements such as AND, OR, NAND/NOR gates, FFs, Mux, RAMs,

✓ Allow Different Programming **Technologies**

Allow both Matrix and Row**based Architectures**

### Programmable Logic Devices

- Programmable logic devices ( PLDs ) are standard ICs

- Available in standard configurations

- Sold in very high volume to many different customers.

- PLDs may be configured or programmed to create a part customized to a specific application

- PLDs use different technologies to allow programming of the device.

- The important features of PLDs:

- No customized mask layers or logic cells

- Fast design turnaround

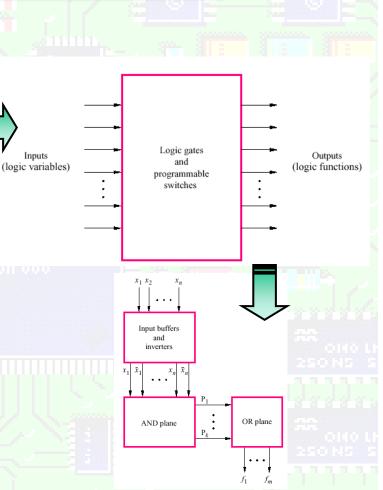

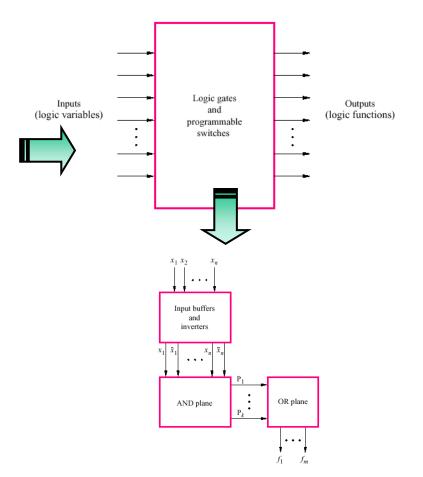

- Structure of programmable logic device (PLD)

- A single large block of programmable interconnect

- A matrix of logic macrocells that usually consist of programmable array logic followed by a flip-flop or latch

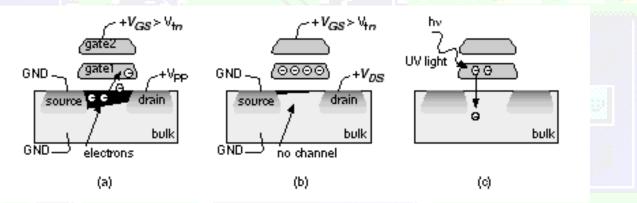

## Examples of PLD

- The simplest type of programmable IC is a **read-only memory ( ROM ).**

- The most common types of ROM use a metal fuse that can be blown permanently

(a programmable ROM or PROM ).

- An eraseable programmable ROM (EPROM), uses programmable MOS transistors whose characteristics are altered by applying a high voltage.

- Erasable PROM

- Erase an EPROM either by using another high voltage (an electrically erasable PROM , or EEPROM )

- Exposing the device to ultraviolet light (UV-erasable PROM, or UVPROM).

- There is another type of ROM that can be placed on any ASIC—a maskprogrammable ROM (mask-programmed ROM or masked ROM).

- A masked ROM is a regular array of transistors permanently programmed using custom mask patterns.

- An embedded masked ROM is thus a large, specialized, logic cell.

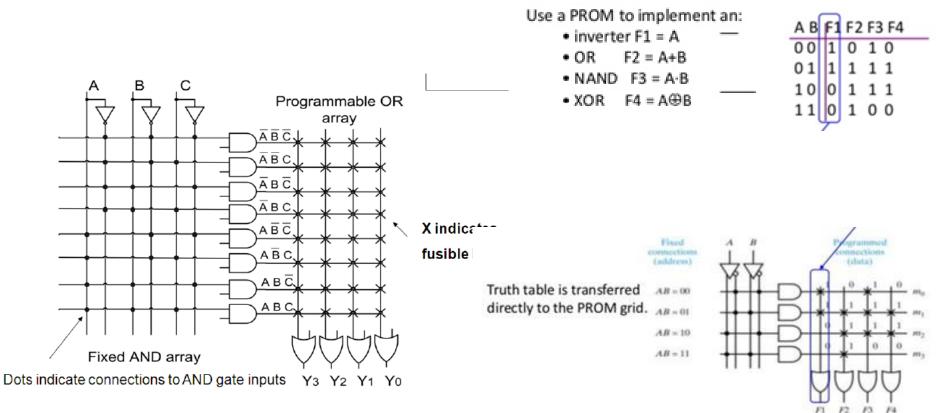

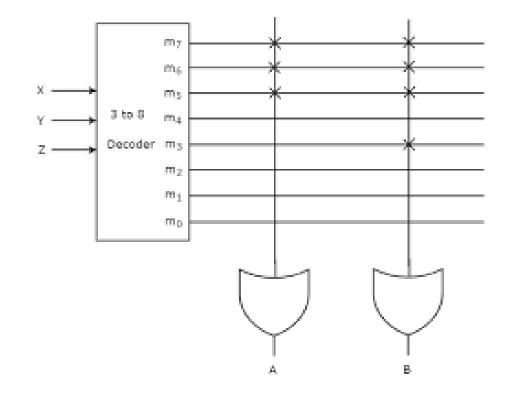

# PROM

### PROM, it is not fast enough. Occupies more space.

# PROM

### Type of PLDs-PLA and PAL

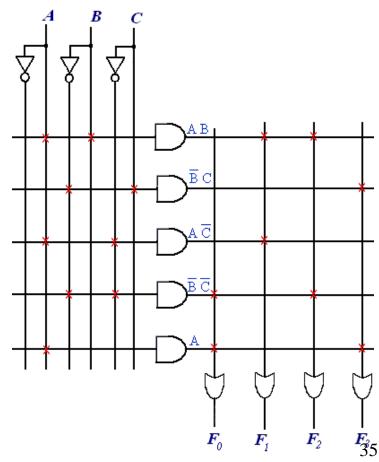

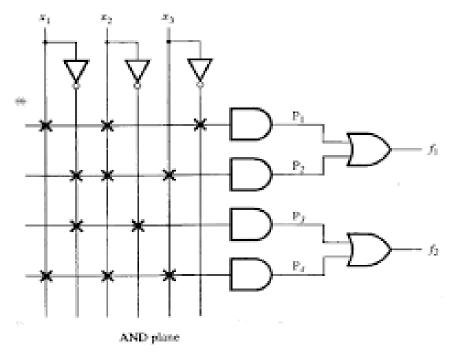

- Place a logic array as a cell on a custom ASIC. This type of logic array is called a **programmable logic array** (PLA).

- A PLA has a programmable AND logic array, or AND plane , followed by a programmable OR logic array, or OR plane

- A PAL has a programmable AND plane and, in contrast to a PLA, a fixed OR plane.

- Depending on how the PLD is programmed, we can have an

- Erasable PLD (EPLD),

- Mask-programmed PLD (called as masked PLD but usually just PLD).

- The first bipolar based PALs, PLAs, and PLDs used p**rogrammable fuses or links**.

- CMOS PLDs usually employ floating-gate transistors

# Programmable Logic Devices

PLA

**PLA Design Example**

# PAL

- Suitable to implement sequential logic.

- Very fast.

# Types of ASICs - Cont'd

Inputs

#### □ Semi-Custom ASICs – Cont'd

#### \* Programmable ASICs

✓ **PLDs** - PLDs are low-density devices which contain 1k - 10 k gates and are available both in bipolar and CMOS technologies [PLA, PAL or GAL]

#### ✓ CPLDs or FPLDs or FPGAs -

FPGAs combine architecture of gate arrays with programmability of PLDs.

#### ✓ User Configurable

✓ Contain Regular Structures circuit elements such as AND, OR, NAND/NOR gates, FFs, Mux, RAMs,

✓ Allow Different Programming **Technologies**

Allow both Matrix and Row**based Architectures**

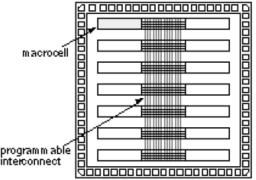

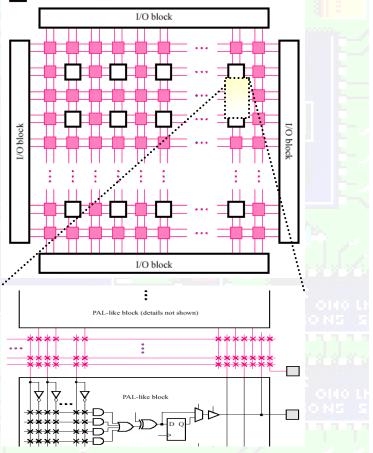

## Essential characteristics of FPGA

- Core-regular array of Programmable basic logic cells implement combinational or sequential logic

- Matrix of programmable interconnects surround the basic logic cells

- Programmable I/O cells surround the core

- A method of programming the basic logic cells and interconnect

- None of the mask layers are customized

- Design turnaround is few hours.

- Difference between PLD and FPGA:

- FPGA are larger and more complex than PLD

# Why FPGA-based ASIC Design?

### □ Choice is based on Many Factors ;

- Speed

- ✤ Gate Density

- ✤ Development Time

- Prototyping and Simulation Time

- Manufacturing Lead Time

- Future Modifications

- Inventory Risk

- Cost

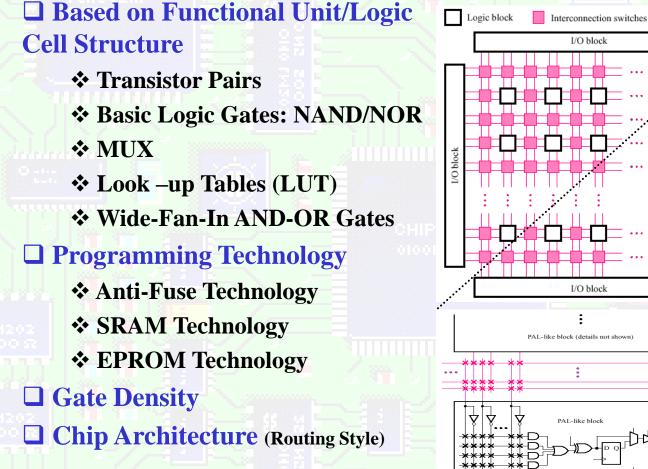

# **Different Categorizations of FPGAs**

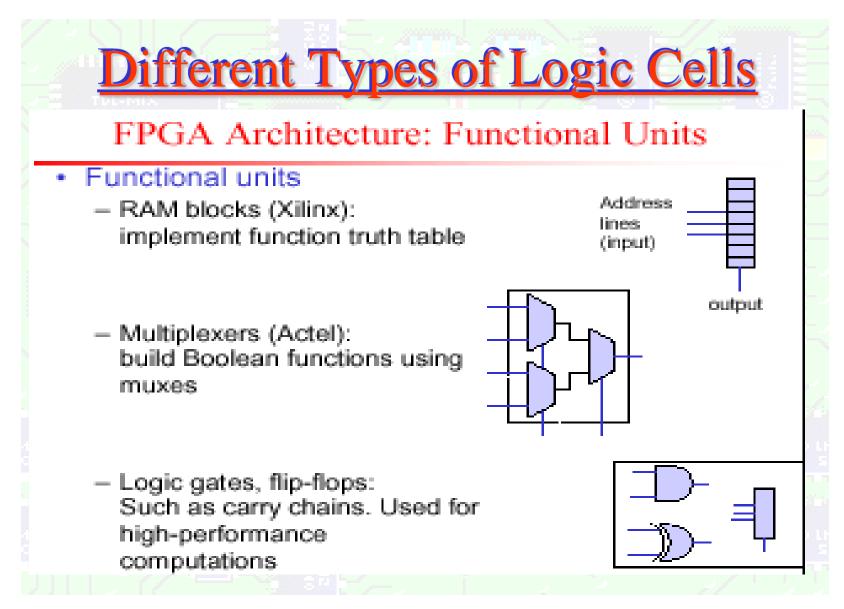

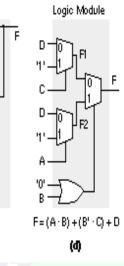

# Different Types of Logic Cells - Cont'd

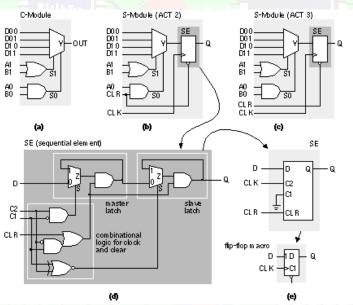

### **Actel Act Logic Module Structure**

**\*** Use Antifuse Programming Tech.

Logic Module

(b)

- \* Based on Channeled GA Architecture

- \* Logic Cell is MUX which can be configured as multi-input logic gates

Logic Module

B1

SB

S0 S1

Actel AC1

(a)

(c)

AO

The Actel ACT 2 and ACT 3 Logic Modules. (a) The C-Module for combinational logic. (b) The ACT 2 S-Module. (c) The ACT 3 S-Module. (d) The equivalent circuit (without buffering) of the SE (sequential element). (e) The sequential element configured as a positive-edge-triggered D flip-flop. (Source: Actel.)

# Different Types of Logic Cells - Cont'd

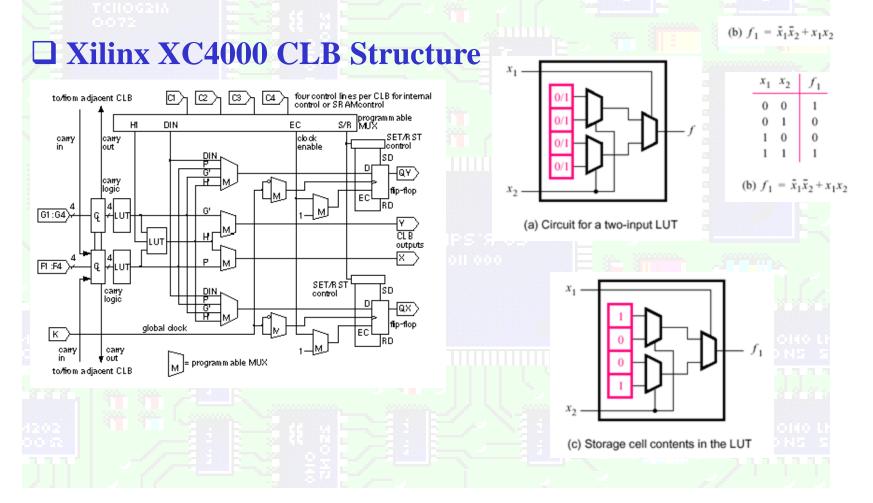

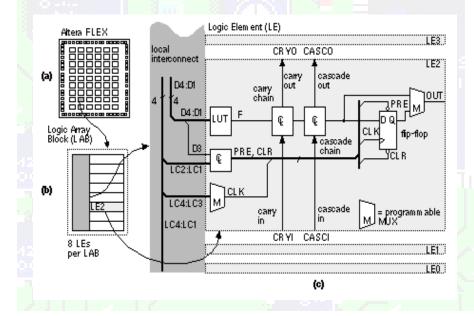

### **Altera Flex / Max Logic Element Structure**

✤Flex 8k/10k Devices – SRAM Based LUTs, Logic Elements (LEs) are similar to those used in XC5200 FPGA

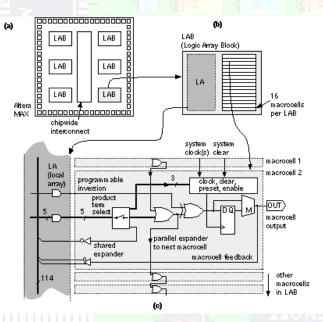

The Altera MAX architecture. (a) Organization of logic and interconnect. (b) A MAX family LAB (Logic Array Block). (c) A MAX family macrocell. The macrocell details vary between the MAX families—the functions shown here are closest to those of the MAX 9000 family

# Different Types of Logic Cells - Cont'd

# To SUMMARIZE, FPGAs from various vendors differ in their

Architecture (Row Based or Matrix Based Routing Mechanism)

- **Gate Density** (Cap. In Equiv. 2- Input NAND Gates)

- Basic Cell Structure

- Programming Technology

| Vendor/ Product | Architechture | Capacity  | Basic Cell | Programming Technology |

|-----------------|---------------|-----------|------------|------------------------|

| Actel           | Gate Array    | 2-8 k     | MUX        | Antifuse               |

| QuickLogic      | Matrix        | 1.2-1.8 k | MUX        | Antifuse               |

| Xilinx          | Matrix        | 2-10 k    | RAM Block  | SRAM                   |

| Altera          | Extended PLA  | 1-5k      | PLA        | EPROM                  |

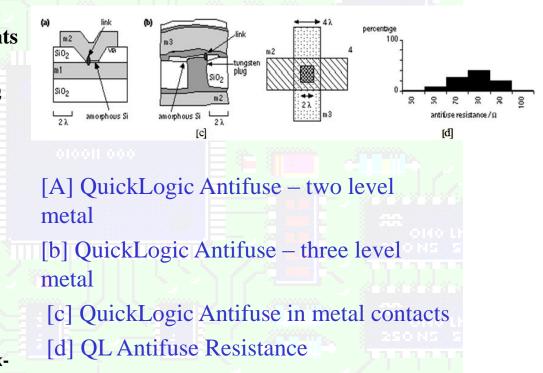

# Antifuse

[b]

## Programming Technologies - Cont'd

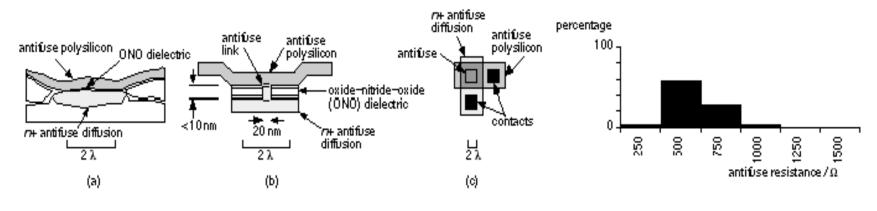

### □ The Antifuse Technology

Invented at Stanford and developed by Actel

Opposite to regular fuse Technology

Normally an open circuit until a programming current (about 5 mA) is forced through it

#### **\***Two Types:

#### \*Actel's PLICE

[[Programmable Low-Impedance Circuit Element]-

\*A High-Resistance Poly-Diffusion Antifuse

ONO layer offers high resistance

For 5mA, resistance is 500Ω

#### Programming time-5-10 Minutes

#### \*Disadvantages:

✤It doesn't allow large amount of current

Need extra space to connect withh metal layer- add parasitic capacitance.-Unwanted Long Delay.

OTP

[A] Actel Antifuse cross section

[b] Link in Actel Antifuse

[c] Actel Antifuse in metal contacts

[d] Actel Antifuse Resistance

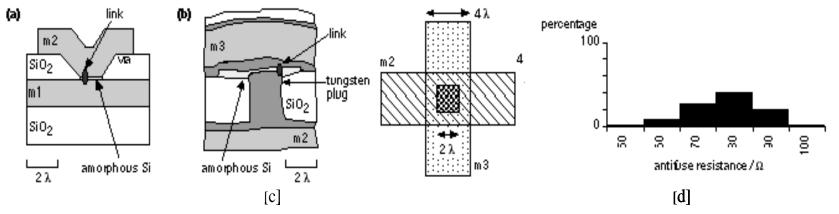

## Programming Technologies - Cont'd

**&QuickLogic's** Low-Resistance metal-metal antifuse [ViaLink] technology

\*Direct metal-2-metal connections

\*Higher programming currents reduce antifuse resistance

\*For 15mA, resistance is 80 Ω

#### **\***Advantage:

\*No parasitic capacitancereduce delay

# Disadvantages of Antifuse technology:

Unwanted RC Delay

OTP Technology

Less reliable- electromigration

Need separate programming box-Activator.

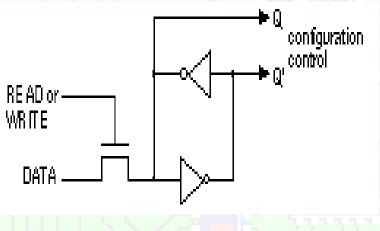

### Programming Technologies – Cont'd □ Static RAM Technology

#### SRAM cells are used for

✓ As Look-Up Tables (LUT) to implement logic (as Truth Tables)

✓ As embedded RAM blocks (for buffer storage etc.)

✓ Two cross coupled inverters and a standard CMOS process

✓ The configuration cell make or break connection

$\checkmark$  As control to routing and configuration switches

#### Advantages

✓ Allows In-System Programming (ISP)

✓ Suitable for Reconfigurable HW

#### Disadvantages

✓ Volatile – needs power all the time / use PROM to download configuration data

✓ Larger in size than Antifuse

# Programming Technologies - Cont'd

#### **EPROM and EEPROM Technology-(Altera & Xilinx)**

**\* EPROM Cell is almost as small as Antifuse**

#### \* Floating-Gate Avalanche MOS (FAMOS) Tech.

- $\checkmark$ Under normal voltage, transistor is on

- $\checkmark$  With Programming Voltage applied, we can turn it off (configuration) to implement our logic

- ✓ Exposure to UV lamp (one hour) we can erase the programming

- ✓ Use EEPROM for quick reconfiguration, also, ISP possible

# Programming Technologies - Cont'd

### **Summary Sheet**

#### Programmable ASIC technologies

|                                                 | Actel                                                         | Xilinx LCA <sup>1</sup>                                 | Altera EPLD                                                                                   | Xilinx EPLD                                                                          |

|-------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Programming<br>technology                       | Poly-diffusion<br>antifuse, PLICE                             | Erasable SRAM<br>ISP                                    | UV-erasable<br>EPROM (MAX 5k)                                                                 | UV-erasable<br>EPROM                                                                 |

|                                                 |                                                               |                                                         | EEPROM (MAX<br>7/9k)                                                                          |                                                                                      |

| Size of                                         | Small but requires                                            | Two inverters plus                                      |                                                                                               | One n-channel                                                                        |

|                                                 | contacts to metal                                             | pass and switch                                         | EPROM device.                                                                                 | EPROM device.                                                                        |

| element                                         |                                                               | devices. La.rgest.                                      | Medium.                                                                                       | Medium.                                                                              |

| Process                                         | Special: CMOS<br>plus three extra<br>masks.                   | Standard CMOS                                           | Standard EPROM<br>and EEPROM                                                                  | Standard EPROM                                                                       |

| Program-<br>ming method                         | Special hardware                                              | PC card, PIROM,<br>or serial port                       | ISP (MAX 9k) or<br>EPROM program-                                                             | EPROM program-<br>mer                                                                |

| -                                               |                                                               | -                                                       | mer                                                                                           |                                                                                      |

| -                                               | QuickLogic                                                    | Crosspoint                                              | mer<br>Atmel                                                                                  | Altera FLEX                                                                          |

| Programming                                     |                                                               | Crosspoint<br>Metal-polysilicon                         |                                                                                               | Altera FLEX<br>Erasable SRAM.                                                        |

| Programming                                     |                                                               |                                                         | Atmel                                                                                         |                                                                                      |

|                                                 | Metal-metal                                                   | Metal-polysilicon                                       | Atmel<br>Erasable SRAM.<br>ISP.<br>Two inverters plus                                         | Erasable SRAM.<br>ISP.<br>Two inverters plus                                         |

| technology                                      | Metal-metal<br>antifuse, ViaLink                              | Metal-polysilicon<br>antifuse                           | Atmel<br>Erasable SRAM.<br>ISP.<br>Two inverters plus<br>pass and switch                      | Erasable SRAM.<br>ISP.<br>Two inverters plus<br>pass and switch                      |

| technology<br>Size of                           | Metal-metal<br>antifuse, ViaLink                              | Metal-polysilicon<br>antifuse                           | Atmel<br>Erasable SRAM.<br>ISP.<br>Two inverters plus                                         | Erasable SRAM.<br>ISP.<br>Two inverters plus                                         |

| technology<br>Size of<br>programming            | Metal-metal<br>antifuse, ViaLink                              | Metal-polysilicon<br>antifuse                           | Atmel<br>Erasable SRAM.<br>ISP.<br>Two inverters plus<br>pass and switch                      | Erasable SRAM.<br>ISP.<br>Two inverters plus<br>pass and switch                      |

| technology<br>Size of<br>programming<br>element | Metal-metal<br>antifuse, ViaLink<br>Smallest<br>Special, CMOS | Metal-polysilicon<br>antifuse<br>Small<br>Special, CMOS | Atmel<br>Erasable SRAM.<br>ISP.<br>Two inverters plus<br>pass and switch<br>devices. Largest. | Erasable SRAM.<br>ISP.<br>Two inverters plus<br>pass and switch<br>devices. Largest. |

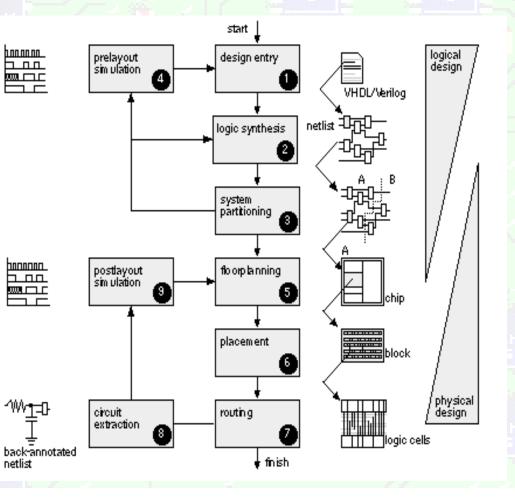

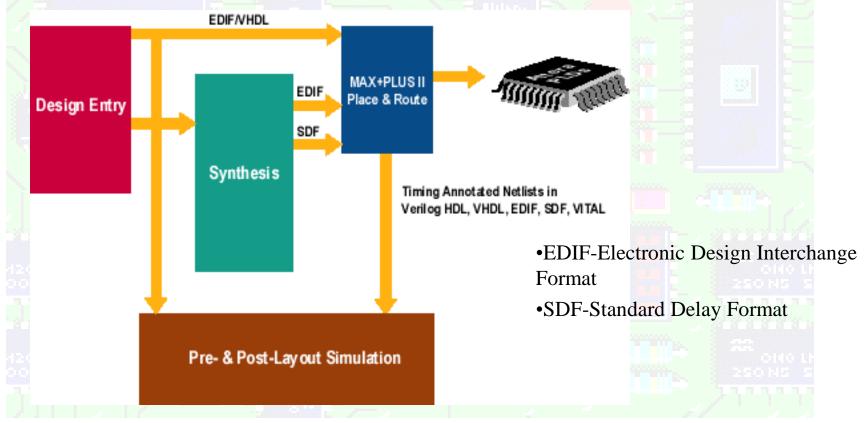

**ASIC Design Process**

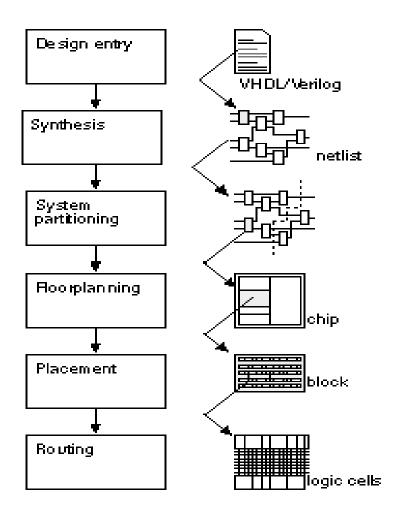

S-1 Design Entry: Schematic entry or HDL description

S-2: Logic Synthesis: Using Verilog HDL or VHDL and Synthesis tool, produce *a netlist*logic cells and their interconnect detail

**S-3 System Partitioning:** Divide a large system into ASIC sized pieces

S-4 Pre-Layout Simulation: Check design functionality

**S-5 Floorplanning:** Arrange netlist blocks on the chip

S-6 Placement: Fix cell locations in a block

S-7 Routing: Make the cell and block interconnections

S-8 Extraction: Measure the interconnect R/C cost

**S-9 Post-Layout Simulation**

# ASIC Design Flow

*Enter the design into an ASIC design system, either* 1.Design entry. using a hardware description language (HDL) or schematic entry. Use an HDL (VHDL or Verilog) and a logic synthesis 2. Logic synthesis. *tool to p*roduce a **netlist** —a description of the logic cells and their connections. 3. System partitioning. *Divide a large system into ASIC-sized pieces.* 4. *Prelayout simulation*. *Check to see if the design functions correctly.* 5. Floorplanning. Arrange the blocks of the netlist on the chip. Decide the locations of cells in a block. 6. Placement. Make the connections between cells and blocks. 7. Routing. 8. Extraction. Determine the resistance and capacitance of the interconnect. 9. Postlayout simulation. *Check to see the design still works with the added loads* of the interconnect.

Steps 1–4 are part of logical design, and steps 5–9 are part of physical design.

• There is some overlap. For example, system partitioning might be considered as either logical or physical design. To put it another way, when we are performing system partitioning we have to consider both logical and physical factors. 55

# ASIC Design Process - Cont'd

□ Altera FPGA Design Flow – A Self-Contained System that does all from Design Entry, Simulation, Synthesis, and Programming of Altera Devices

# ASIC Design Process - Cont'd

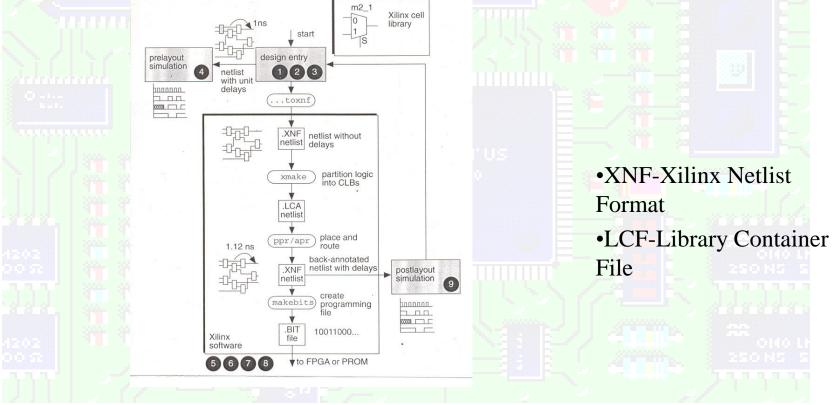

#### □ Xilinx FPGA Design Flow – Allows Third-Party Design Entry SW, Accepts their generated netlist file as an input

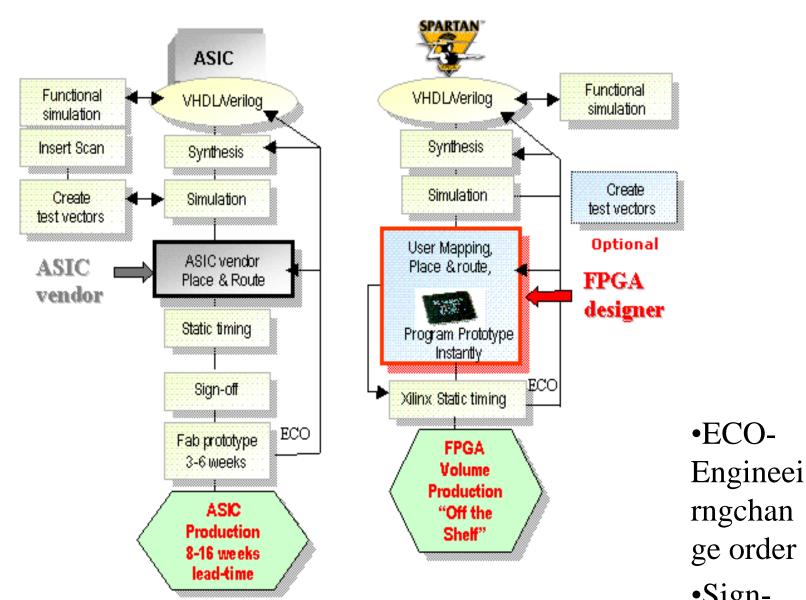

## FPGA vs. ASIC

#### FPGA

#### Advantages:

- Faster time-to-market

- No NRE (Non Recurring Expenses)

- Simpler design cycle

- More predictable project cycle

- Field Re-programability

- Reusability

- Prototyping

- Unlike ASICs, FPGA's have special handwares such as Block-RAM, DCM modules, MACs, memories and high speed I/O, embedded CPU etc inbuilt

- FPGA synthesis is much more easier than ASIC.

#### Disadvantages

- Higher unit cost

- Slow... difficult to achieve high frequency

- Power consumption in FPGA is more. You don't have any control over the power optimization. This is where ASIC wins the race !

- You have to use the resources available in the FPGA. Thus FPGA limits the design size.

#### ASIC

#### Advantages

- Cost....cost....Lower unit costs

- Speed...speed....ASICs are faster than **F**PGA

- Low power....Low power....Low power

- ASIC you can implement analog circuit, mixed signal designs. This is generally not possible in FPGA.

- In ASIC DFT (Design For Test) is inserted. In FPGA DFT is not carried out (rather for FPGA no need of DFT !) .

#### Disadvantages

- Nonger Time-to-market Nigh NRE

- Design Issues such as DFM, SI

- In FPGA you don't have all these because ASIC designer takes care of all these. (Don't forget FPGA is an IC and designed by ASIC design engineer !!)

- Expensive Tools: ASIC design tools are very much expensive. You spend a huge amount of NRE.

## FPGA Vs ASIC Design Flow

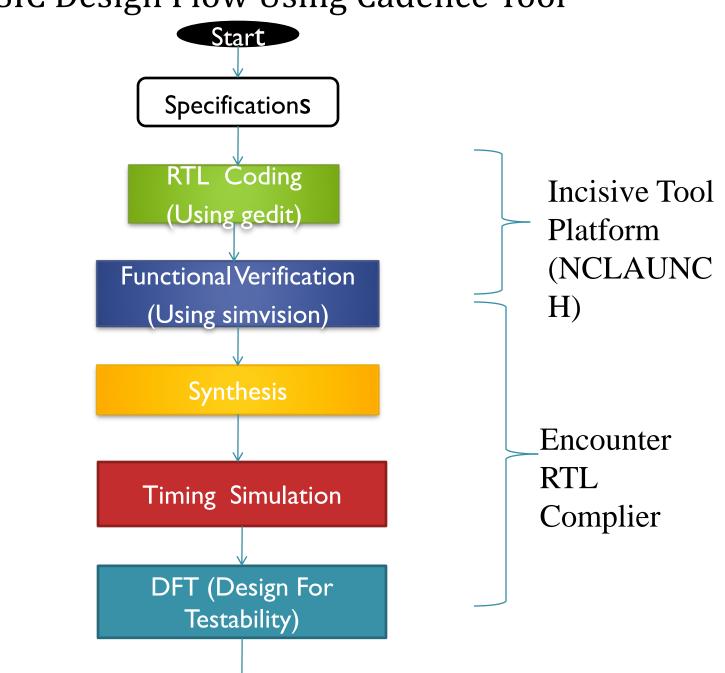

### ASIC Design Flow Using Cadence Tool

# UNIT I & II ASIC Construction & System Partitioning

Dr.K.Kalyani AP, ECE, TCE

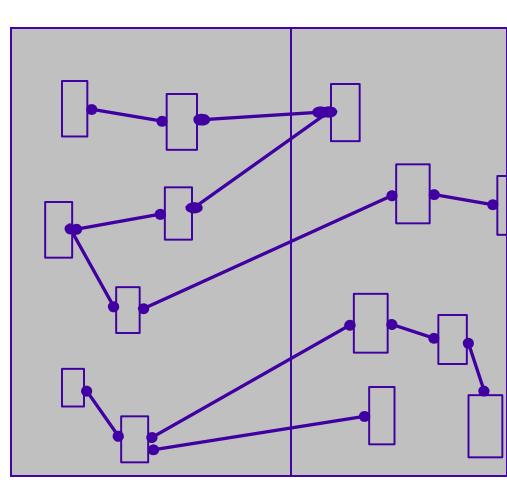

# **Physical Design Steps**

- Part of an ASIC design flow showing the system partitioning, floorplanning, placement, and routing steps.

- Performed in a slightly different order, iterated or omitted depending on the type and size of the system and its ASICs.

- Floorplanning assumes an increasingly important role.

- Sequential-Each of the steps shown in the figure must be performed and each depends on the previous step.

- Parallel- However, the trend is toward completing these steps in a parallel fashion and iterating, rather than in a sequential manner.

# **CAD** Tools

#### System partitioning:

- Goal. Partition a system into a number of ASICs.

- Objectives.

- Minimize the number of external connections between the ASICs.

- Keep each ASIC smaller than a maximum size.

#### Floor planning:

- Goal. Calculate the sizes of all the blocks and assign them locations.

- **Objective.** Keep the highly connected blocks physically close to each other.

#### **Placement:**

- Goal. Assign the interconnect areas and the location of all the logic cells within the flexible blocks.

- **Objectives.** Minimize the ASIC area and the interconnect density.

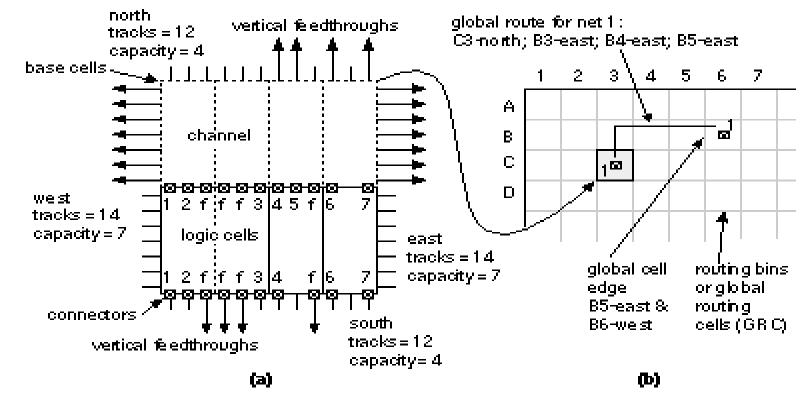

#### **Global routing:**

- Goal. Determine the location of all the interconnect.

- **Objective.** Minimize the total interconnect area used.

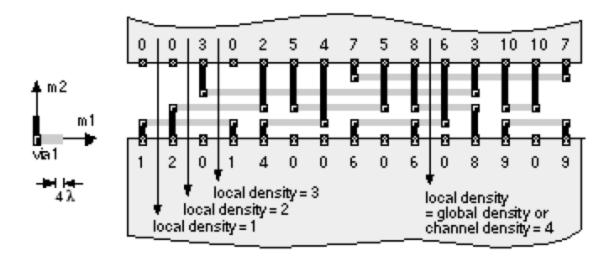

#### **Detailed routing:**

- Goal. Completely route all the interconnect on the chip.

- **Objective.** Minimize the total interconnect length used.

## Methods and Algorithms

- Each of the ASIC physical design steps, in general, belongs to a class of mathematical problems known as NP-complete problems.

- **Definition** : This means that it is unlikely we can find an algorithm to solve the problem exactly in polynomial time.

- **Polynomial:** If the time it takes to solve a problem increases with the size of the problem at a rate that is polynomial but faster than quadratic (or worse in an exponential fashion).

- A CAD tool needs methods or algorithms to generate a solution to each problem using a reasonable amount of computer time.

## **Measurement or objective function**

#### Measurement or objective function:

We need to make a quantitative measurement of the quality of the solution that we are able to find.

Often we combine several parameters or metrics that measure our goals and objectives into a measurement function or Objective function.

#### **Cost Function :**

If we are minimizing the measurement function, it is a cost function.

#### **Gain function :**

If we are maximizing the measurement function, we call the function a gain function (sometimes just gain).

# **ASIC Physical steps**

- Each step of ASIC physical design steps are solved by:

- A set of goals and objectives

- A way to measure the goals and objectives

- Algorithm or method to find a solution that meets the goals and objectives.

## **VLSI** Physical Design :- Partitioning

#### System partitioning requires

- Goals and Objectives

- Methods and algorithms to find solutions

- Ways to evaluate these solutions.

#### Goal of partitioning

– Divide the system into number of small systems.

#### Objectives of Partitioning

we may need to take into account any or all of the following objectives:

- A maximum size for each ASIC

- A maximum number of ASICs

- A maximum number of connections for each ASIC

- A maximum number of total connections between all ASICs

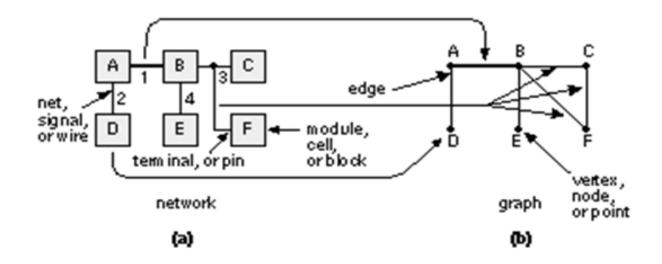

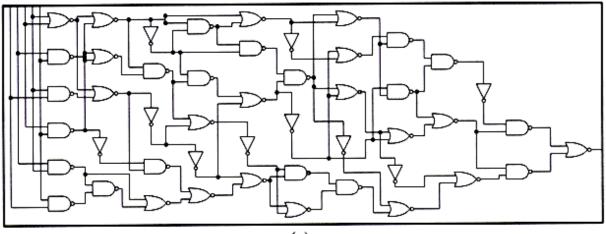

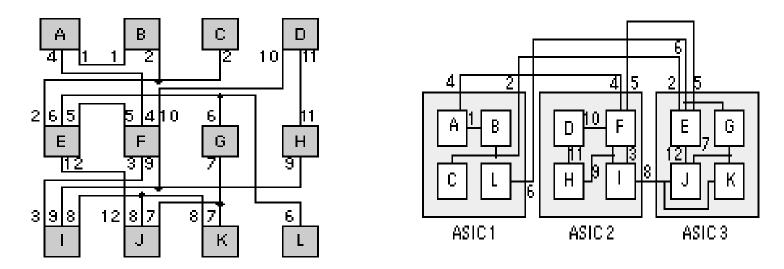

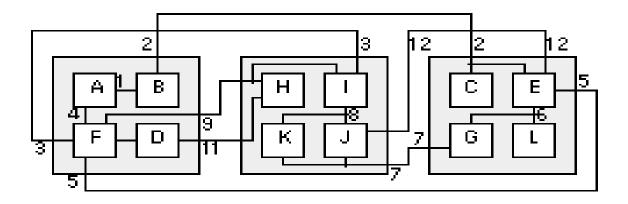

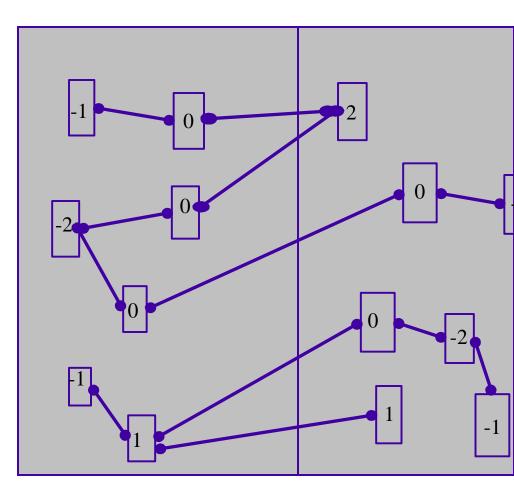

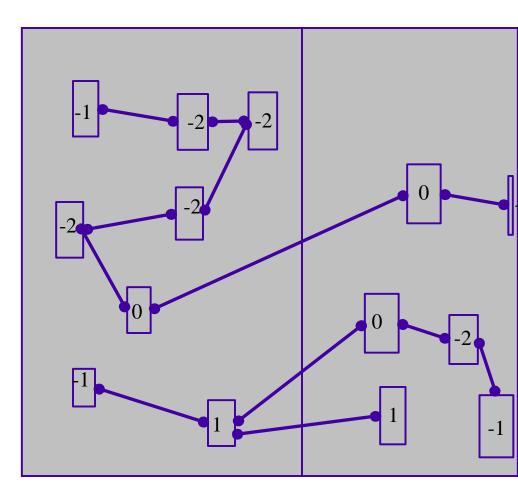

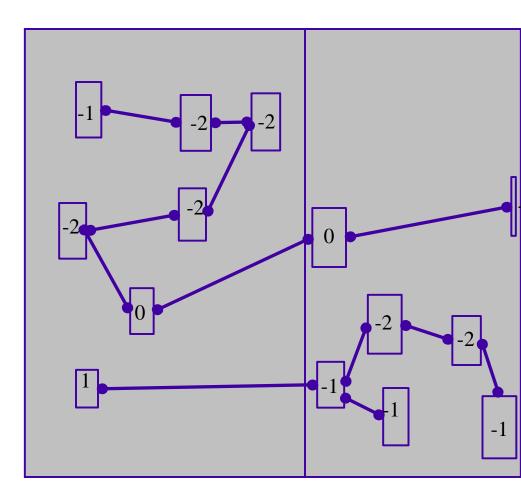

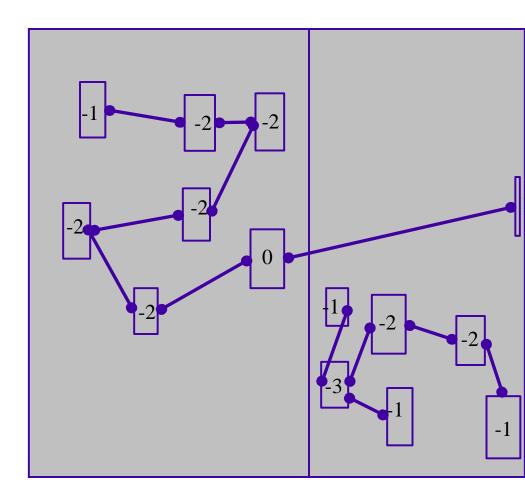

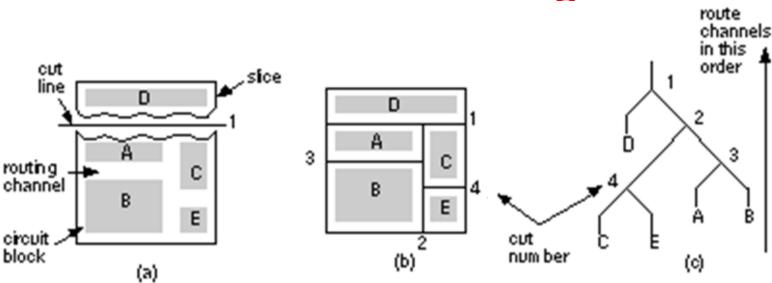

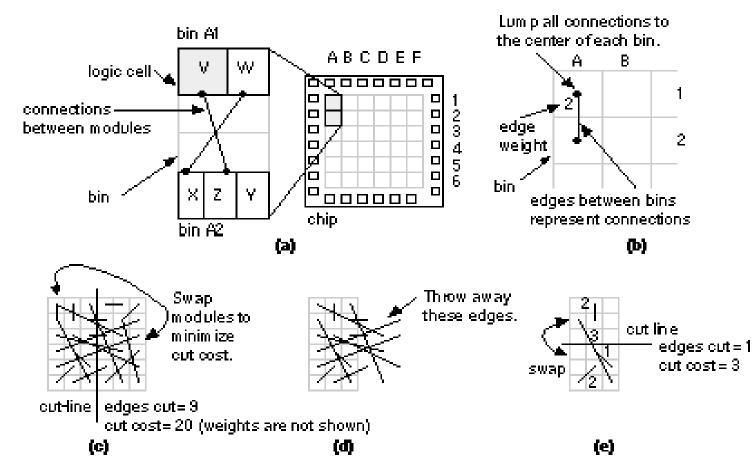

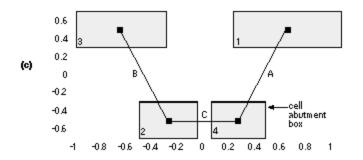

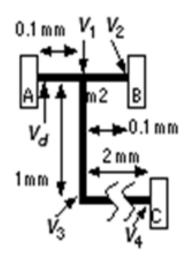

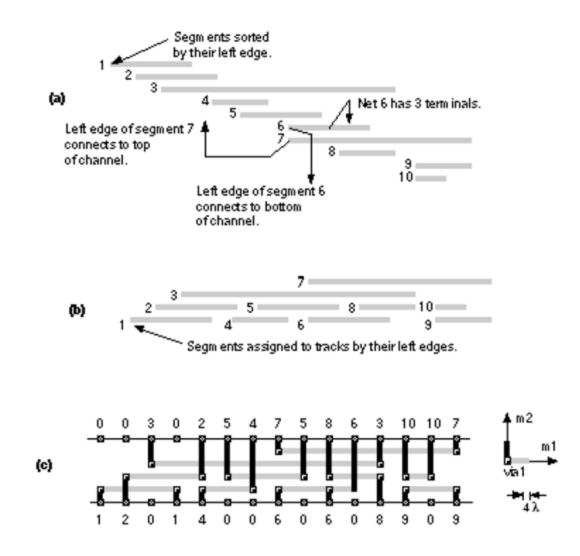

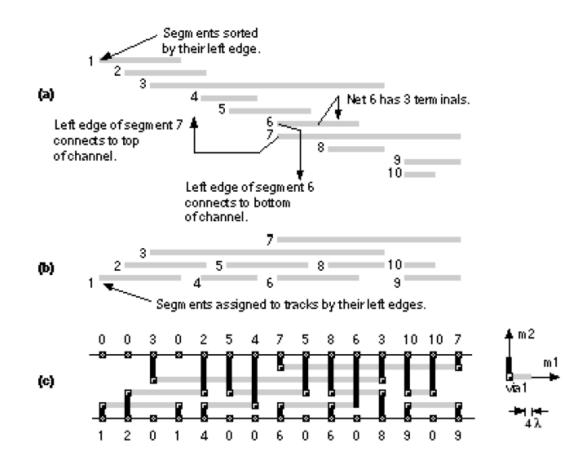

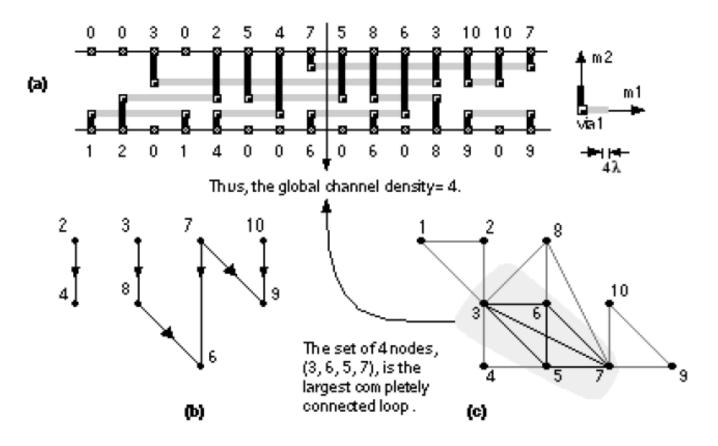

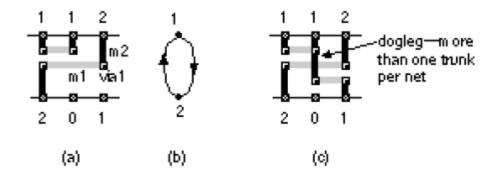

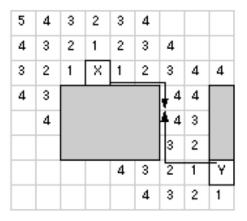

- Figure (a) shows a circuit schematic, netlist, or network.

- The network consists of circuit modules A–F. Equivalent terms for a circuit module cell, logic cell, macro, or a block.

- A cell or logic cell -a small logic gate (NAND etc.), collection of other cells;

- Macro gate-array cells;

- Block a collection of gates or cells.

- Each logic cell has Electrical connections between the terminalsconnectors or pins.

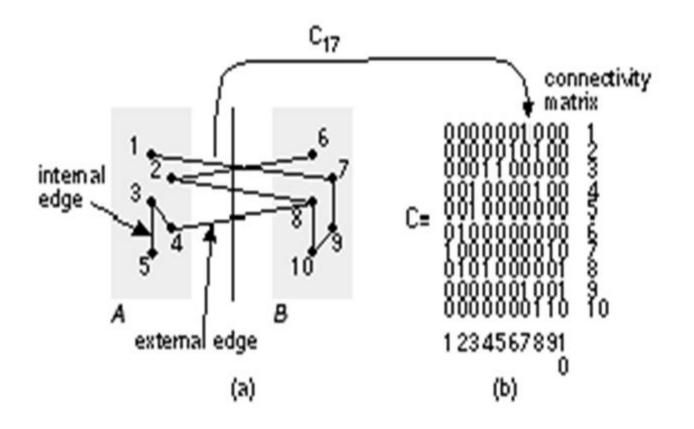

- The network can be represented as the mathematical graph shown in Figure (b).

- A graph is like a spider's web:

- it contains vertexes (or vertices) A–F -graph nodes or points) that are connected by edges.

- A graph vertex corresponds to a logic cell.

- An electrical connection (a net or a signal) between two logic cells corresponds to a graph edge.

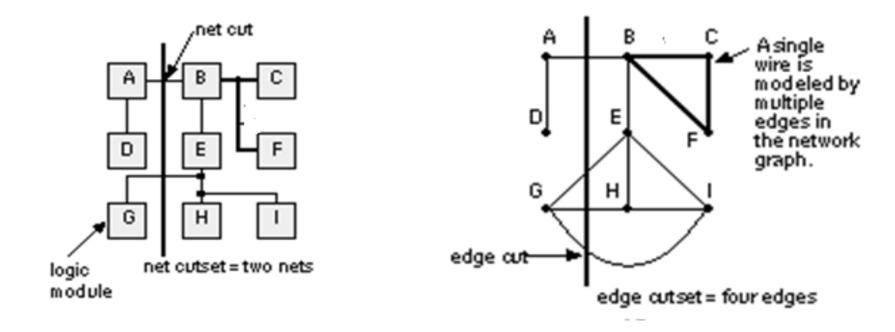

- Net Cutset

- Divide the network into two by drawing a line across connections, make net cuts. The resulting set of net cuts is the net cutset.

- Number of net cuts the number of external connections between the two partitions in a network.

- Edge cutset.

- When we divide the network graph into the same partitions we make edge cuts and we create the edge cutset.

- Number of edge cuts the number of external connections between the two partitions in a graph

- Number of edge cuts in a graph is not necessarily equal to the number of net cuts in the network.

•72

- Estimate the die size of a 40 k-gate ASIC in a 0.35 µm gate array, three-level metal process with 166 I/O pads.

- Die size includes core size and I/O size.

- Core size(logic and routing)=(gates/gate density) ×routing factor ×(1/gate array utilization)

- Gate density=standard cell density ×gate array utilization

- I/O size =  $a^2$  where a is the one side of die.

- One side of die= No of I/O pads in a side × I/O pad pitch

#### 1µm(micron)=0.0393701mil

(1mil= Thousands of inch)

| Parameter                                                                | Typical value                                                                                      | Comment                                                                                                   | Scaling          |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------|

| Lambda, λ                                                                | 0.5 μm=0.5 (minimum feature size)                                                                  | In a 1µm technology, $\lambda \approx 0.5 \ \mu$ m.                                                       | NA               |

| Effective gate length                                                    | 0.25 to 1.0µm                                                                                      | Less than drawn gate length, usually by about 10 percent.                                                 | λ                |

| I/O-pad width (pitch)                                                    | 5 to 10mil<br>=125 to 250μm                                                                        | For a 1 $\mu m$ technology, 2LM ( $\lambda$ =0.5 $\mu m$ ). Scales less than linearly with $\lambda.$     | λ                |

| I/O-pad height                                                           | 15 to 20mil<br>=375 to 500μm                                                                       | For a 1 $\mu m$ technology, 2LM ( $\lambda$ =0.5 $\mu m$ ). Scales approximately linearly with $\lambda.$ | λ                |

| Large die                                                                | 1000 mil/side, 10 <sup>6</sup> mil <sup>2</sup>                                                    | Approximately constant                                                                                    | 1                |

| Small die                                                                | 100 mil/side, 10 <sup>4</sup> mil <sup>2</sup>                                                     | Approximately constant                                                                                    | 1                |

| Standard-cell density                                                    | 1.5×10 <sup>-3</sup> gate/μm <sup>2</sup><br>=1.0gate/mil <sup>2</sup>                             | For 1 $\mu$ m, 2LM, library<br>= 4 × 10 <sup>-4</sup> gate/ $\lambda^2$ (independent of scaling).         | 1/λ <sup>2</sup> |

| Standard-cell density                                                    | 8×10 <sup>−3</sup> gate/μm <sup>2</sup><br>= 5.0gate/mil <sup>2</sup>                              | For 0.5 $\mu$ m, 3LM, library<br>= 5×10 <sup>-4</sup> gate/ $\lambda^2$ (independent of scaling).         | 1/λ <sup>2</sup> |

| Gate-array utilization                                                   | 60 to 80%                                                                                          | For 2LM, approximately constant                                                                           | 1                |

|                                                                          | 80 to 90%                                                                                          | For 3LM, approximately constant                                                                           | 1                |

| Gate-array density                                                       | $\begin{array}{l} (0.8 \text{ to } 0.9) \times \text{standard} \\ \text{cell density} \end{array}$ | For the same process as standard cells                                                                    | 1                |

| Standard-cell rout-<br>ing factor=(cell<br>area+route<br>area)/cell area | 1.5 to 2.5 (2LM)<br>1.0 to 2.0 (3LM)                                                               | Approximately constant                                                                                    | 1                |

| Package cost                                                             | \$0.01/pin, "penny per<br>pin"                                                                     | Varies widely, figure is for low-cost<br>plastic package, approximately con-                              | 1                |

•74

- For this ASIC the minimum feature size is 0.35 µm.

- Gate Density:

- Gate density=standard cell density ×gate array utilization

gate density =  $0.35 \,\mu$  m standard-cell density  $\infty$  (0.8 to 0.9)

=  $4 \propto 10^{-4}$  to  $4.5 \propto 10^{-4}$  gate/  $\lambda^2$ .

- Core Size

- Core size(logic and routing)=(gates/gate density) ×routing factor ×(1/gate array utilization)

$(4 \approx 10^{4} \text{ gates/gate density}) \approx \text{routing factor} \approx (1/\text{gate-array utilization}) = \frac{4 \approx 10^{4} / (4 \approx 10^{-4} \text{ to } 4.5 \approx 10^{-4}) \approx (1 \text{ to } 2) \approx 1 / (0.8 \text{ to } 0.9) = 10^{8} \text{ to } 2.5 \approx 10^{8} \lambda^{2}$

= 4840 to 11,900 mil<sup>2</sup>.

- Die size

- No of I/O pads=166.

- No of pads per side

- =166/4=42 I/O pads per side.

- If a I/O pad pitch=5 mil then

- One side of die

=5×42=210mil

- Minimum requirement of die size to fit 166 I/O pads =210×210=4.4×10<sup>4</sup>mil<sup>2</sup>

- Die area utilized by core logic

$=1.19 \times 10^{4}/4.4 \times 10^{4}$  mil<sup>2</sup>=27%.

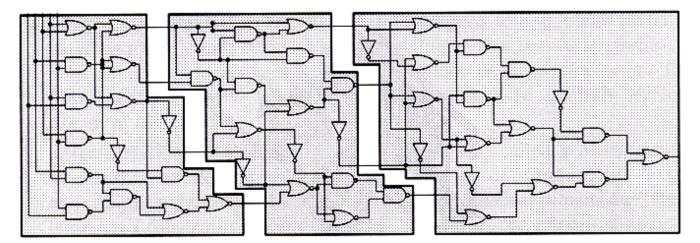

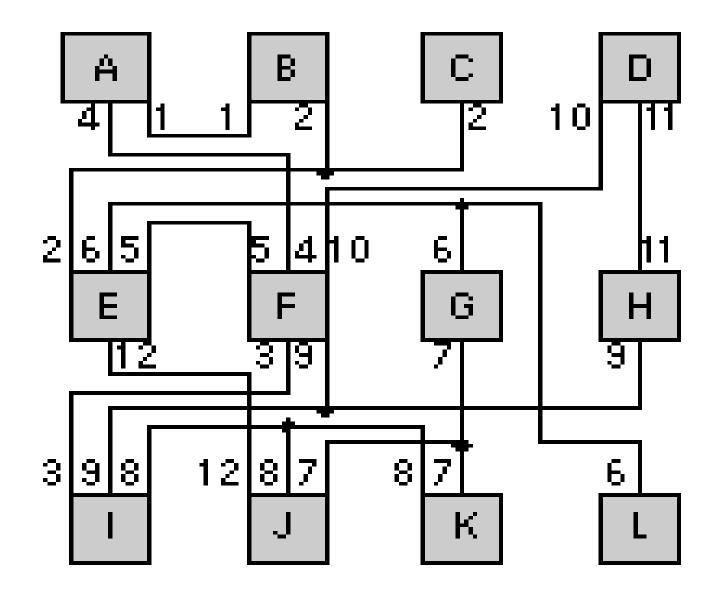

## Partitioning of a Circuit

(a)

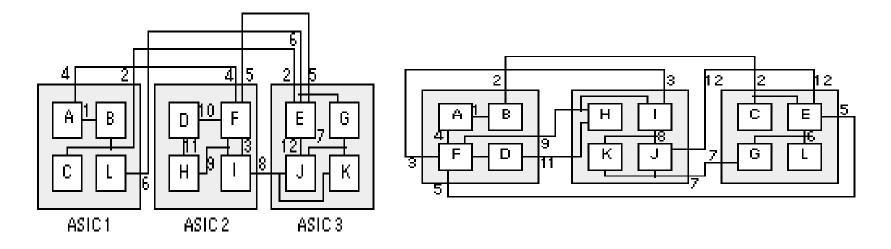

#### A Simple Partitioning Example

•FIGURE 15.7 Partitioning example.

- •Goal: to partition our simple network into ASICS. •(a) We wish to partition this network into three ASICs with no more than four logic cells per ASIC. •(b) percitipvies ware veloce for the end to we jupp (nets 2, 4, 5, 6, and 8)—the minimum number.

- -Use no more than three ASICs.

- -Each ASIC is to contain no more than four logic cells.

• -Use the minimum number of external connections for .78 each ASIC.

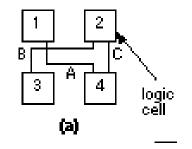

## •Types of Partitioning

- Splitting a network into several pieces network partitioning problem.

- Two types of algorithms used in system partitioning are

- Constructive partitioning uses a set of rules to find a solution.

Iterative partitioning improvement (or iterative partitioning refinement - takes an existing solution and tries to improve it.

#### **Constructive Partitioning**

- The most common constructive partitioning algorithms seed growth or cluster growth.

- The **steps** of a simple seed-growth algorithm for constructive partitioning:

- 1. Start a new partition with a seed logic cell.

- 2. Consider all the logic cells that are not yet in a partition. Select each of these logic cells in turn.

- 3. Calculate a gain function, g(m), that measures the benefit of adding logic cell m to the current partition. One measure of gain is the number of connections between logic cell m and the current partition.

- 4. Add the logic cell with the highest gain g(m) to the current partition.

- 5. Repeat the process from step 2. If you reach the limit of logic cells in a partition, start again at step 1.

## **Constructive Partitioning**

### • Seed Logic cell:

The **logic cell with the most nets** is a good choice as the seed logic cell.

• Cluster:

A set of seed logic cells known as a cluster.

Called as *clique —borrowed from graph* theory.

### • Clique:

A clique of a graph is a subset of nodes where each pair of nodes is connected by an edge

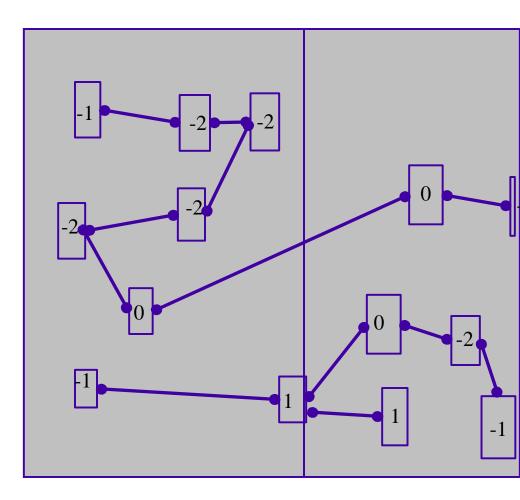

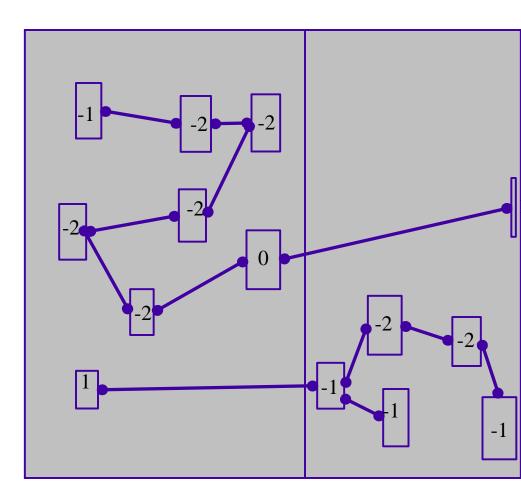

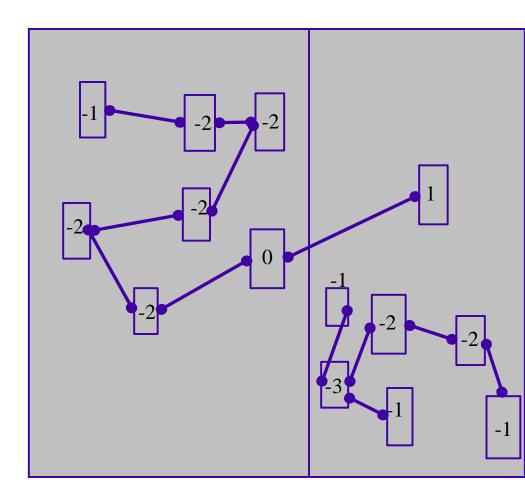

#### **Constructive Partitioning**

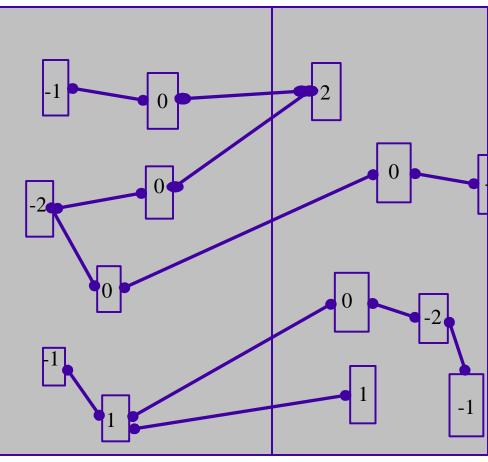

•A constructed partition using logic cell C as a seed. It is difficult to get from this local minimum, with seven external connections (2, 3, 5, 7, 9,11,12), to the optimum solution of b.

## Improvement in Partitioning

Fig 1 with 5 external connections Fig 2 with 7 external connections

- •To get from the solution shown in Fig 2 to the solution of Fig 1, which has a minimum number of external connections, requires a complicated swap.

- •The three pairs: D and F, J and K, C and L need to be swapped <u>\*84</u>

#### Iterative Partitioning Improvement

Algorithm based on Interchange method and group migration method

#### **Interchange method** (swapping a single logic cell):

If the swap improves the partition, accept the trail interchange otherwise select a new set of logic cells to swap.

#### Example: Greedy Algorithm –

It considers only one change

-Rejects it immediately if it is not an improvement.

-Accept the move only if it provides immediate benefit.

It is known as local minimum.

#### **Group Migration** (swapping a group of logic cell):

- Group migration consists of swapping groups of logic cells between partitions.

- The group migration algorithms

- Adv: better than simple interchange methods at improving a solution

- **Disadv:** but are more complex.

#### Example: Kernighan – Lin Algorithm (K-L)

- Min cut Problem : Dividing a graph into two pieces, minimizing the .85 nets(edges) that are cut

### The Kernighan–Lin Algorithm

### The Kernighan–Lin Algorithm (contd.,)

• Total external cost, cut cost, cut weight

$$W = \sum_{a \in A, b \in B} c_{ab}$$

• External edge cost

$$E_a = \sum_{y \in B} c_{ay}$$

• Internal edge cost

$$I_a = \sum_{z \in A} c_{az}$$

• Gain

$$g = D_a + D_b - 2C_{ab}$$

where

$$D_a = E_a - I_a$$

### The Kernighan–Lin Algorithm (contd.,)

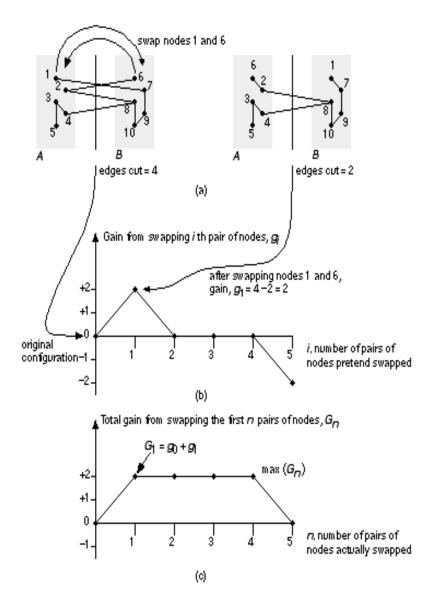

- The K–L algorithm **finds a group of node pairs to swap that increases the gain** even though swapping individual node pairs from that group might decrease the gain.

- The steps of K-L algorithm are:

- 1. Find two nodes,  $a_i$  from A, and  $b_i$  from B, so that the gain from swapping them is a maximum. The gain  $g_i$  is  $g_i = D_{a_i} + D_{b_i} 2C_{a_ib_i}$

- 2. Next pretend swap ai and bi even if the gain  $g_i$  is zero or negative, and do not consider ai and bi eligible for being swapped again.

- 3. Repeat steps 1 and 2 a total of m times until all the nodes of A and B have been pretend swapped. We are back where we started, but we have ordered pairs of nodes in A and B according to the gain from interchanging those pairs.

### The Kernighan–Lin Algorithm (contd.,)

4. Now we can choose which nodes we shall actually swap. Suppose we only swap the first n pairs of nodes that we found in the preceding process. In other words we swap nodes X = a1, a2, &..., an from A with nodes Y = b1, b2,&...,bn from B. The total gain would be,  $G = \sum_{n=1}^{n} g_{n}$

$$G_n = \sum_{i=1}^n g_i$$

- 5. We now choose n corresponding to the maximum value of  $G_n$

- If the maximum value of G<sub>n</sub> > 0, then swap the sets of nodes X and Y and thus reduce the cut weight by G<sub>n</sub>.

- Use this new partitioning to start the process again at the first step.

- If the maximum value of  $G_n = 0$ , then we cannot improve the current partitioning and we stop.

- We have found a locally optimum solution.

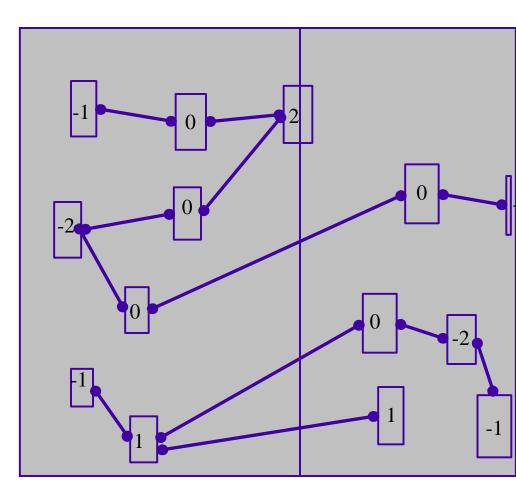

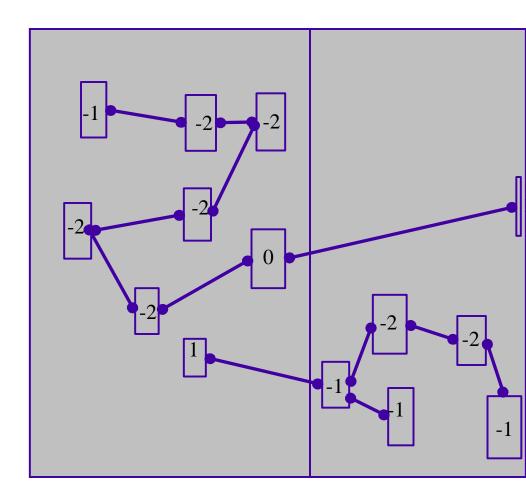

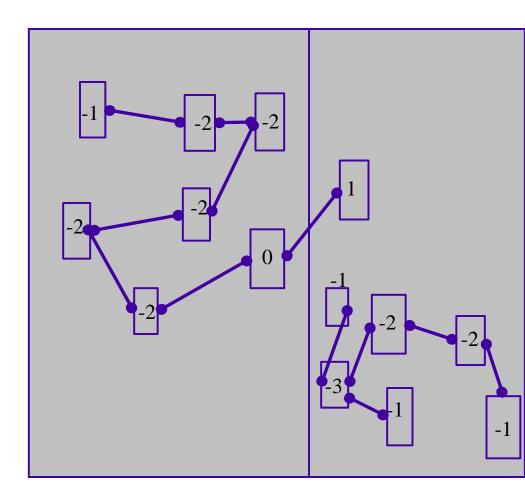

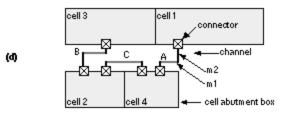

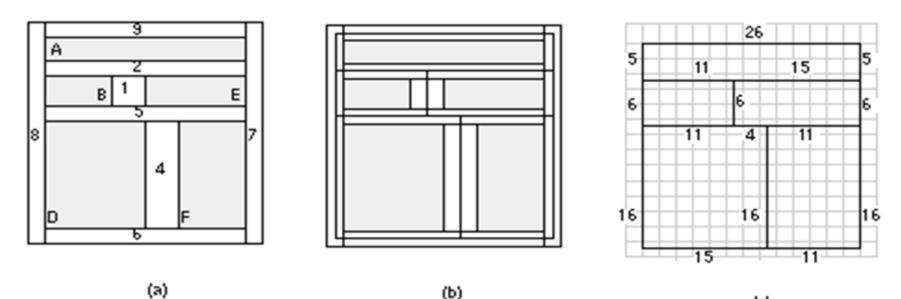

- •FIGURE 15.9 Partitioning a graph using the Kernighan–Lin algorithm.

- •(a) Shows how swapping node 1 of partition A with node 6 of partition B results in a gain of g = 2.

- •(b) A graph of the gain resulting from swapping pairs of nodes.

- •(c) The total gain is equal to the sum of the gains obtained at each step.

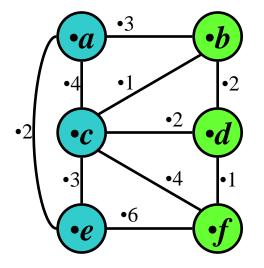

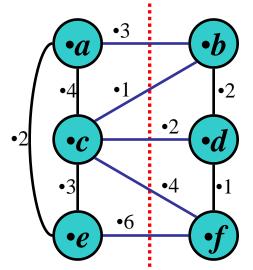

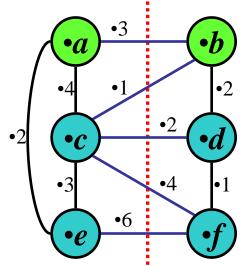

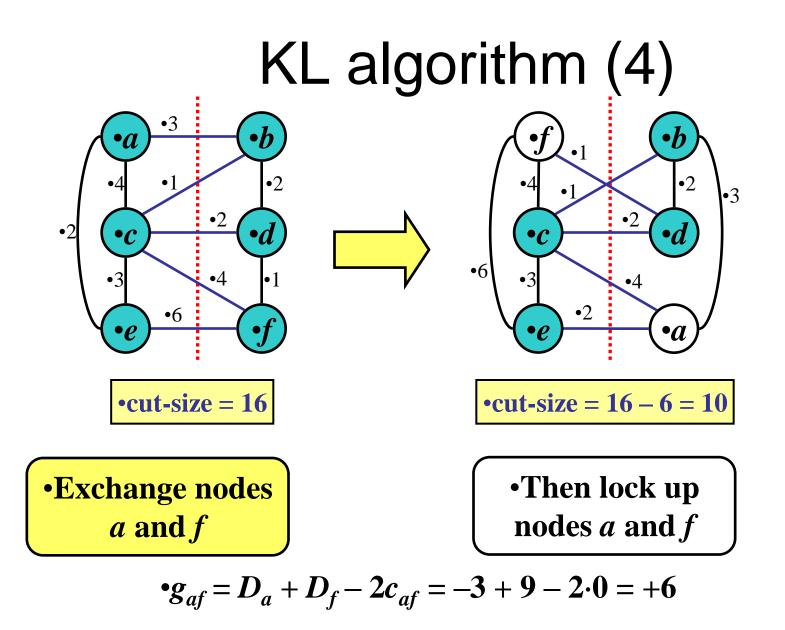

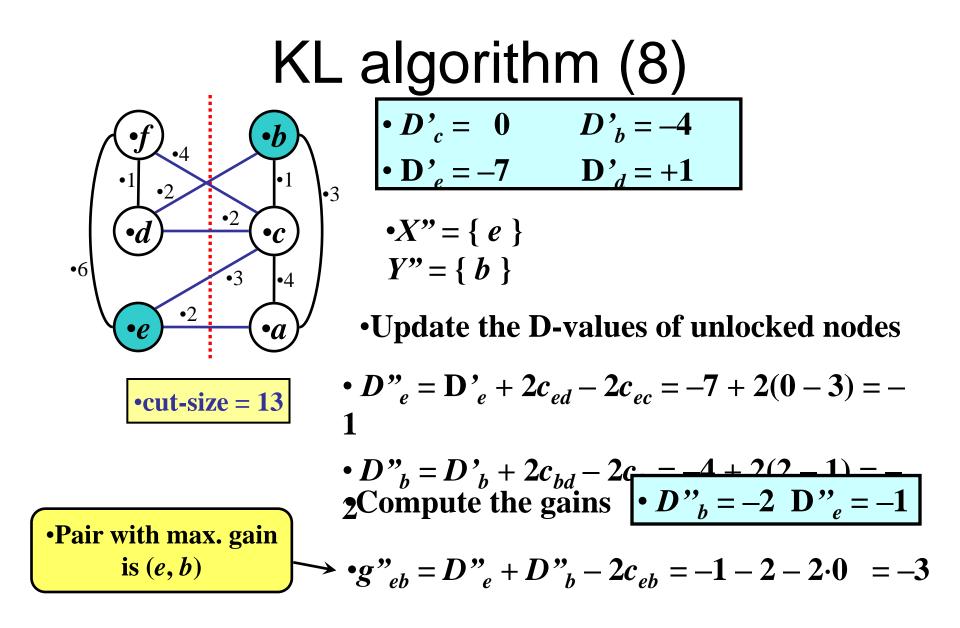

# Kernighan-Lin Algorithm (1)

•Given:

Initial weighted graph G with  $V(G) = \{ a, b, c, d, e, f \}$

•Start with any partition of V(G) into X and Y, say

•

$$X = \{ a, c, e \}$$

$Y = \{ b, d, f \}$

# KL algorithm (2a)

•Compute the gain values of moving node x to the others set:

• $D_x = E_x - I_x$   $E_x = \text{cost of edges connecting node x}$ with the other group (extra)  $I_x = \text{cost of edges connecting node x}$

$I_x = \text{cost of edges connecting node x}$ within its own group (intra)

•cut-size = 3+1+2+4+6 = 16

•

$$X = \{ a, c, e \}$$

$Y = \{ b, d, f \}$

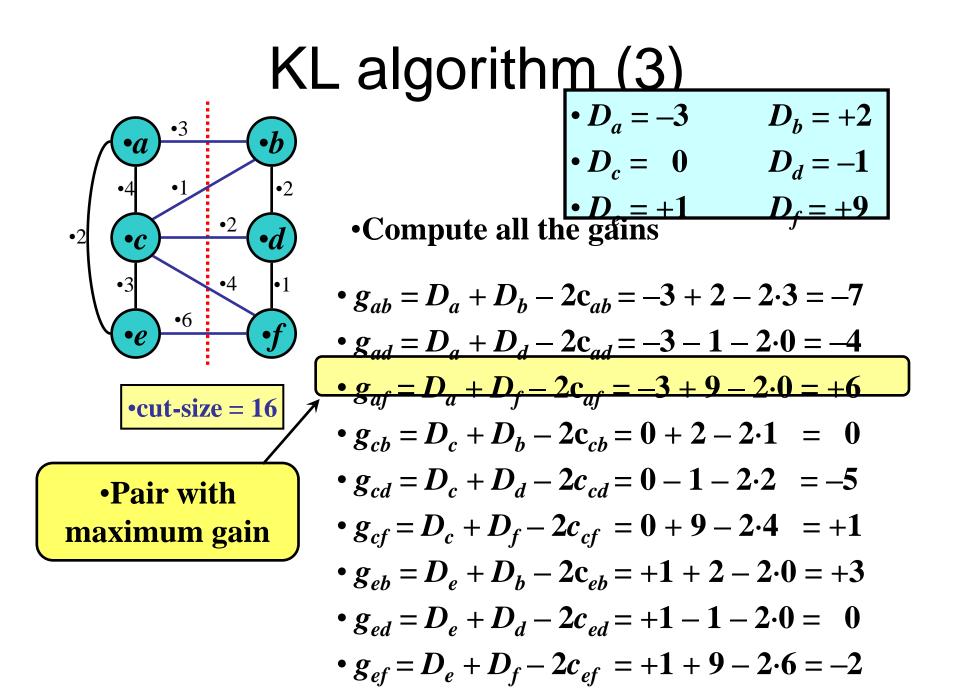

•  $D_a = E_a - I_a = -3 \ (= 3 - 4 - 2)$ •  $D_c = E_c - I_c = 0 \ (= 1 + 2 + 4 - 4 - 3)$ •  $D_e = E_e - I_e = +1 \ (= 6 - 2 - 3)$ •  $D_b = E_b - I_b = +2 \ (= 3 + 1 - 2)$ •  $D_d = E_d - I_d = -1 \ (= 2 - 2 - 1)$ •  $D_f = E_f - I_f = +9 \ (= 4 + 6 - 1)$

# KL algorithm (2b)

•Cost saving when exchanging *a* and *b* is essentially  $D_a + D_b$

•However, the cost saving **3** of the direct edge was counted twice. But this edge still connects the two groups

•Hence, the real "gain" (i.e. cost saving) of this exchange is  $g_{ab} = D_a + D_b - 2c_{ab}$

• $X = \{ a, c, e \}$  $Y = \{ b, d, f \}$  •  $D_a = E_a - I_a = -3$  (= 3 - 4 - 2) •  $D_b = E_b - I_b = +2$  (= 3 + 1 - 2) •  $g_{ab} = D_a + D_b - 2c_{ab} = -7$  (= -3 + 2 - 2·3)

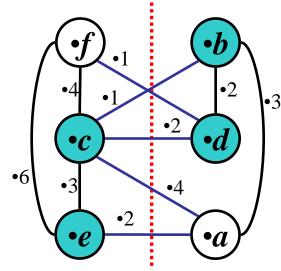

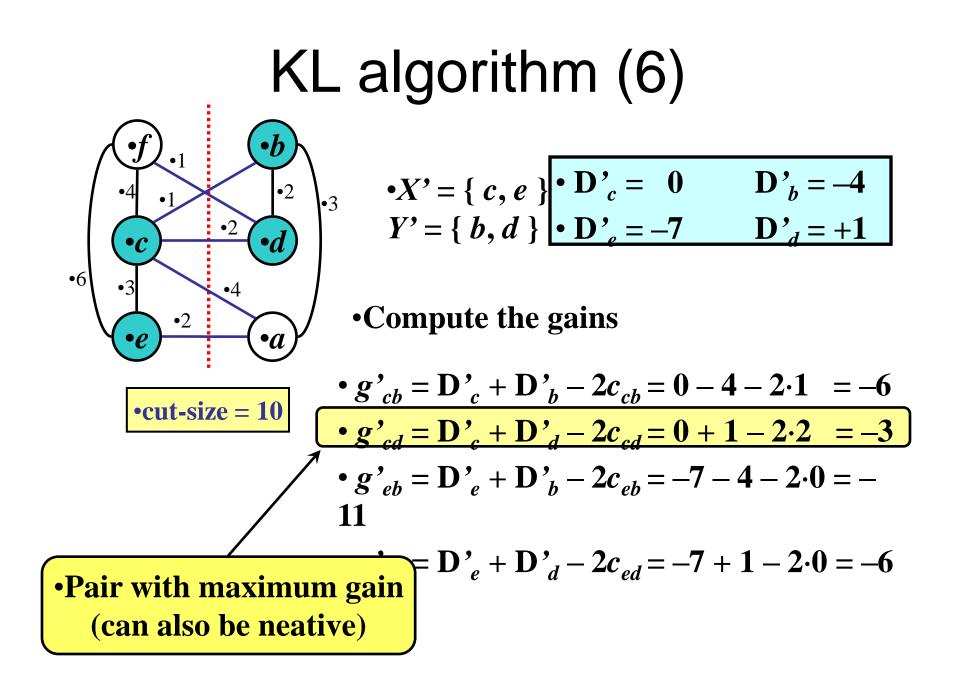

# KL algorithm (5)

•cut-size = 10

•X' = { c, e }

Y' = { b, d }

•

$$D_a = -3$$

$D_b = +2$

•  $D_c = 0$   $D_d = -1$

•  $D_e = +1$   $D_f = +9$

•Update the G-values of unlocked nodes

- $D'_c = D_c + 2c_{ca} 2c_{cf} = 0 + 2(4 4) = 0$

- $D'_e = D_e + 2c_{ea} 2c_{ef} = 1 + 2(2 6) = -7$

- $D'_{b} = D_{b} + 2c_{bf} 2c_{ba} = 2 + 2(0 3) = -4$

- $D'_d = D_d + 2c_{df} 2c_{da} = -1 + 2(1 0) = 1$

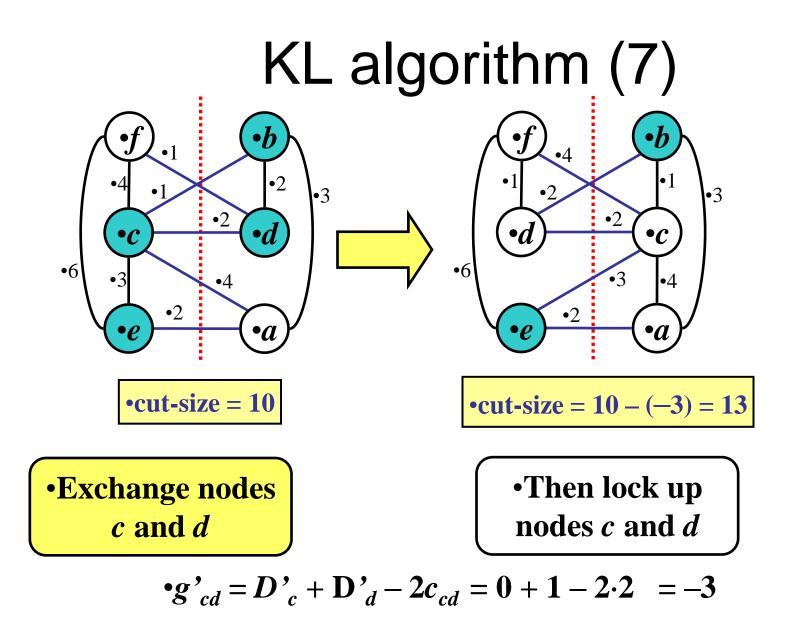

# KL algorithm (9)

• Summary of the Gains...

$$-g = +6$$

$-g + g' = +6 - 3 = +3$

$g + g' + g'' = +6 - 3 = -2$

- -g+g'+g''=+6-3-3=0

- Maximum Gain = g = +6

- Exchange only nodes *a* and *f*.

- End of 1 pass.

#### **Repeat the Kernighan-Lin**.

## **Demerits of Kernighan–Lin Algorithm**

- Minimizes the number of **edges cut**, not the number of nets cut.

- Does not directly allow for **more than two partitions**.

- Does not allow logic cells to be **different sizes**.

- Does not allow partitions to be **unequal** or find the optimum partition size.

- Does not allow for selected logic cells to be fixed in place.

- K-L Finding local optimum solution in **random fashion**

- Random starting partition

- Choice of nodes to swap may have equal gain

- Expensive in computation time.

- An amount of computation time that grows as  $n^2 \log n$  for 2n nodes.

#### Solution:

To implement a net-cut partitioning rather than an edge-cut partitioning, keep track of the nets rather than the edges -FM algorithm

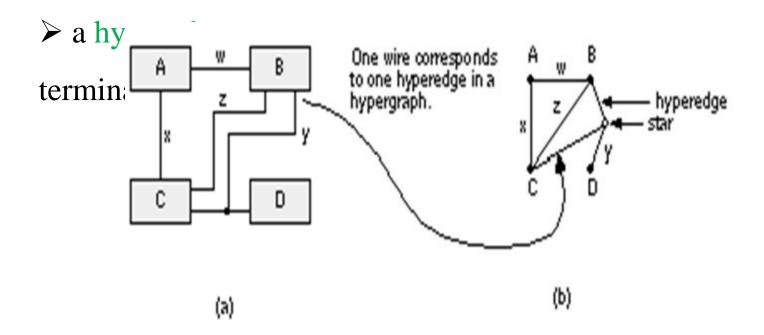

•Hypergraph- To represent nets with multiple terminals in a Hypergraph network accurately

•A hypergraph consist of –

$\succ$  a star- a special type of vertex

•FIGURE - A hypergraph. (a) The network contains a net y with three terminals. (b) In the network hypergraph we can model net y by a single hyperedge (B, C, D) and a star node. Now there is a direct correspondence between wires or nets in the network and hyperedges in the graph<sub>2</sub>

### Fiduccia-Mattheyses (F-M) Algorithm

- Addresses the difference between nets and edges.

- Reduce the computational time.

#### **Key Features of F-M:**

- **Base logic cell** Only one logic cell moves at a time.

- Base logic cell is chosen to maintain **balance** between partitions in order to stop the algorithm from moving all the logic cells to one large partition

- Balance the ratio of total logic cell size in one partition to the total logic cell size in the other. Altering the balance allows us to vary the sizes of the partitions.

- **Critical nets** used to simplify the gain calculations.

- A net is a **critical net** if it has an attached logic cell that, when swapped, changes the number of nets cut.

- It is only necessary to recalculate the gains of logic cells on critical nets that are attached to the base logic cell.

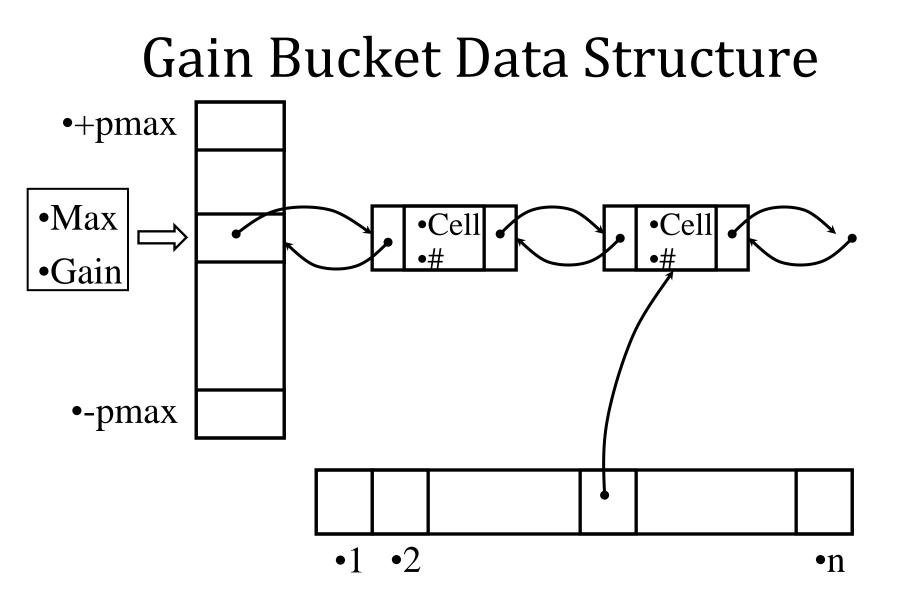

- The logic cells that are free to move are stored in a doubly linked list. The lists are sorted according to gain. This allows the logic cells with maximum gain to be found quickly.

- **Reduce the computation time** increases only slightly more than linearly with the number of logic cells in the network.

## **Features of FM Algorithm**

- Modification of KL Algorithm:

- Can handle non-uniform vertex weights (areas)

- Allow unbalanced partitions

- Extended to handle hypergraphs

- Clever way to select vertices to move, run much faster.

## Ideas of FM Algorithm

- Similar to KL:

- Work in passes.

- Lock vertices after moved.

- Actually, only move those vertices up to the maximum partial sum of gain.

- Difference from KL:

- Not exchanging pairs of vertices.

- Move only one vertex at each time.

- The use of gain bucket data structure.

#### FM Partitioning:

Moves are made based on object gain

Object Gain: The amount of change in cut crossings that will occur if an object is moved from its current partition into the other partition

- each object is assigned a gain

- objects are put into a sorted gain list

- the object with the highest gain from the larger of the two sides is selected and moved.

- the moved object is "locked"

- gains of "touched" objects are recomputed

- gain lists are resorted

## FM Partitioning:

## FM Partitioning:

Moves are made based on object gain.

Object Gain: The amount of change in cut crossings that will occur if an object is moved from its current partition into the other partition

- Each object is assigned a gain

- Objects are put into a sorted gain list

- The object with the highest gain from the larger of the two sides is selected and moved.

- the moved object is "locked"

- gains of "touched" objects are recomputed

- gain lists are resorted

### FM Partitioning:

# **Time Complexity of FM**

- For each pass,

- Constant time to find the best vertex to move.

- After each move, time to update gain buckets is proportional to degree of vertex moved.

- Total time is O(p), where p is total number of pins

- Number of passes is usually small.

## **Overcome problems in K-L using F-M** algorithm

- To generate unequal partitioning

- **Dummy logic cells** with no connections introduced in K-L algorithm

- Adjust partition size according to balance parameter in F-M algorithm

- To fix logic cells in place during partitioning

- That logic cells should not be considered as base logic cells in F-M algorithm.

## **Ratio-Cut Algorithm**

- Removes the restriction of constant partition sizes.

- The **cut weight W** for a cut that divides a network into two partitions, A and B , is given by ,

$$W = \sum_{a \in A, b \in B} c_{ab}$$

• The **ratio of a cut** is defined as

$\mathbf{R} = \mathbf{W} / (|\mathbf{A}| |\mathbf{B}|)$

The |A| and |B| are size of a partition is equal to the number of nodes it contains (also known as the set cardinality). The cut that minimizes R is called the ratio cut.

# **Ratio-Cut Algorithm (contd.,)**

- A network is partitioned into small, highly connected groups using ratio cuts.

- A reduced network is formed from these groups.

—Each small group of logic cells forms a node in the reduced network.

- Finally, apply the F–M algorithm to improve the reduced network

#### **Difference of Ratio-cut than K-L**

The K–L algorithm minimizes W while keeping partitions A and B the same size.

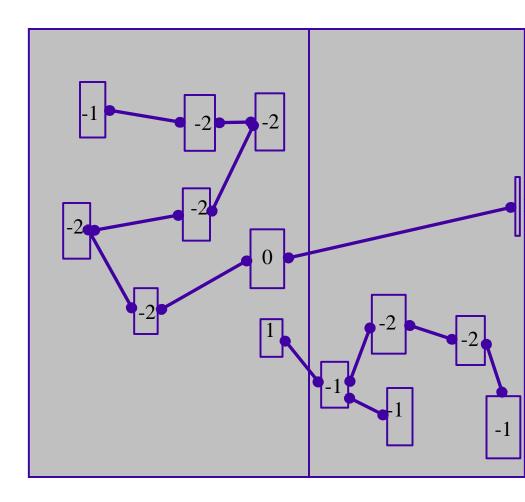

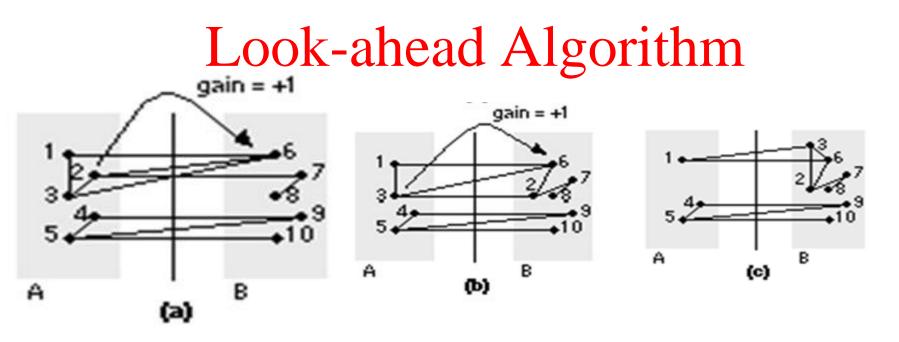

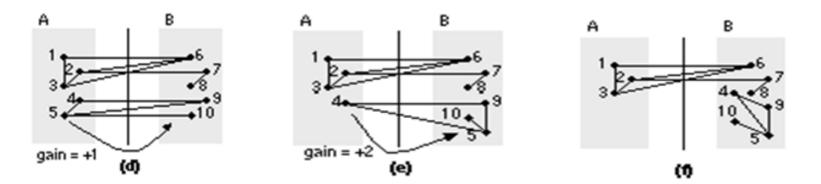

## **Look-ahead Algorithm**

#### Why Look-ahead?

- **K–L and F–M algorithms consider only the immediate gain** to be made by moving a node.

- When there is a tie between nodes with equal gain (as often happens), there is no mechanism to make the best choice.

#### Algorithm

- The gain for the initial move is called as the **first-level gain**.

- Gains from subsequent moves are then **second-level and higher gains**.

- Define a **gain vector** that contains these gains.

- The choice of nodes to be swapped are found Using the gain vector .

- This **reduces both the mean and variation** in the number of cuts in the resulting partitions.

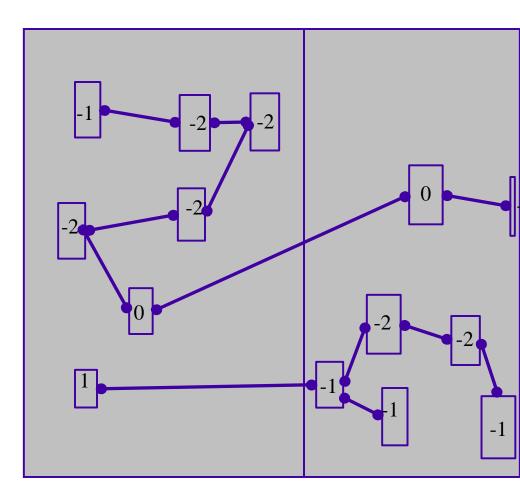

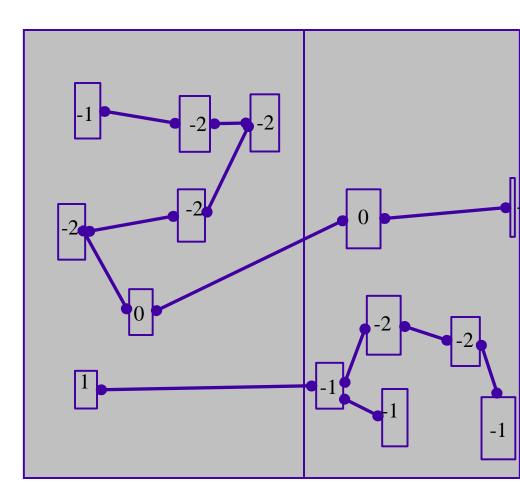

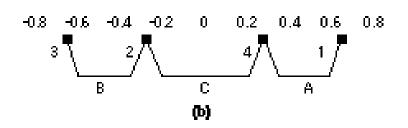

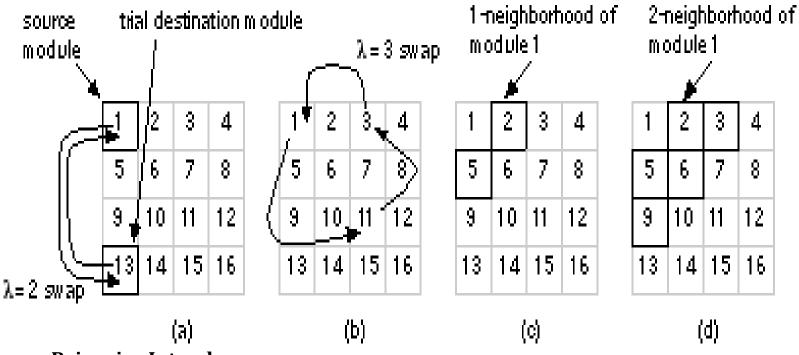

• Gain vector: Move 2 to B=+1, Move 3 to B=+1

• Gain vector: Move 5 to B=+1, Move 4 to B=+2

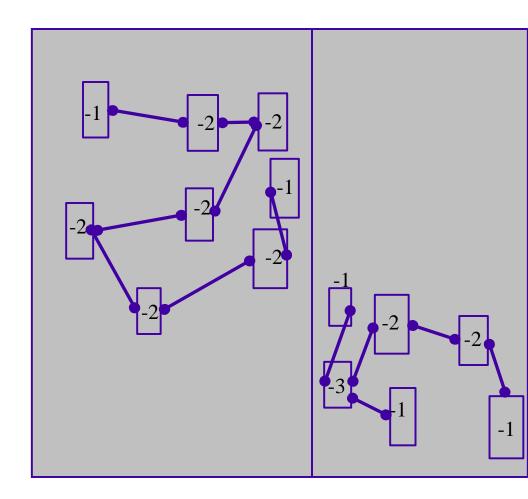

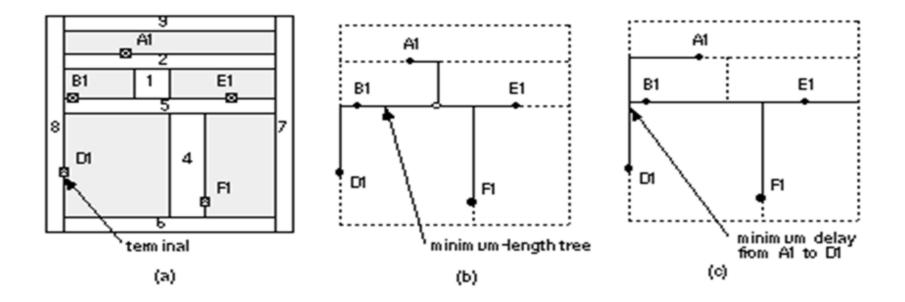

# Look-ahead Algorithm (contd.,)

- •An example of network partitioning that shows the need to look ahead when selecting logic cells to be moved between partitions.

- •Partitionings (a), (b), and (c) show one sequence of moves Partition I

- •Partitionings (d), (e), and (f) show a second sequence Partition II

#### •Partition I:

•The partitioning in (a) can be improved by moving node 2 from A to B with a gain of 1. The result of this move is shown in (b). This partitioning can be improved by moving node 3 to B, again with a gain of 1.

#### •Partition II:

•The partitioning shown in (d) is the same as (a). We can move node 5 to B with a gain of 1 as shown in (e), but now we can move node 4 to B with a gain of 2

# Simulated Annealing

- Takes an existing solution and then makes successive changes in a series of random moves.

- Each move is accepted or rejected based on an **energy function**.

- In the Interchange method,

- Accept the new trial configuration only if the energy function decreases,

- which means the new configuration is an improvement

- But in the **simulated Annealing**,

- Accept the new configuration even if the energy function increases for the new configuration—which means things are getting worse.

- The probability of accepting a worse configuration is controlled by the exponential expression  $exp(-\Delta E / T)$ ,

where,  $\Delta \mathbf{E}$  - the resulting increase in the energy function.

T - a variable that can be controlled and corresponds to the temperature in the annealing of a metal cooling (this is why the process is called simulated annealing).

### **Simulated Annealing**

• A parameter that relates the temperatures,  $T_i$  and  $T_{i+1}$ , at the i th and i + 1 th iteration:

$T_{i+1} = \alpha T_i$  .

- As the temperature is slowly decreased, the probability of making moves that increase the energy function gets decreased.

- **Cooling schedule** The critical parameter of the simulated-annealing algorithm is the rate at which the temperature T is reduced.

- Finally, as the **temperature approaches zero**, refuse to make any moves that increase the energy of the system and the system falls and comes to rest at the **nearest local minimum**.

- The **minimums of the energy function** correspond to possible solutions.

- The best solution is the **global minimum**.

## **Simulated Annealing**

- Requirement of Simulated Annealing:

- To find a good solution, a local minimum close to the global minimum, requires a **high initial temperature and a slow cooling schedule**.

- Disadvantage:

- This results in many trial moves and very long computer run time.(it gives optimum)

- Advantage:

- To solve large graph problems

- Hill climbing- Accept moves that seemingly take us away from a desirable solution to allow the system to escape from a local minimum and find other, better, solutions.

#### Other Partitioning Objectives

| Constraints or<br>Objectivies | Purpose                                                                                                                                                 | Implemented                                                                                                                                                      |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timing Constraints            | certain logic cells in a system<br>may need to be located on<br>the same ASIC in order to avoid<br>adding the delay of any external<br>interconnections | Adding weights to nets to make<br>them more important than others.                                                                                               |

| Power Constraints             | Some logic cells may consume<br>more power than others                                                                                                  | To assign more than rough estimates<br>of power consumption for each logic<br>cell at the system planning stage,<br>before any simulation has been<br>completed. |

| Technology Constraints        | To include memory on an ASIC                                                                                                                            | It will keep logic cell together<br>requiring similar technology                                                                                                 |

| Cost Constraints              | To use low cost package                                                                                                                                 | To keep ASICs below a certain size.                                                                                                                              |

| Test Constraints              | Maintain Observability and<br>Controllability                                                                                                           | It require that we force certain<br>connection to external<br>•135                                                                                               |

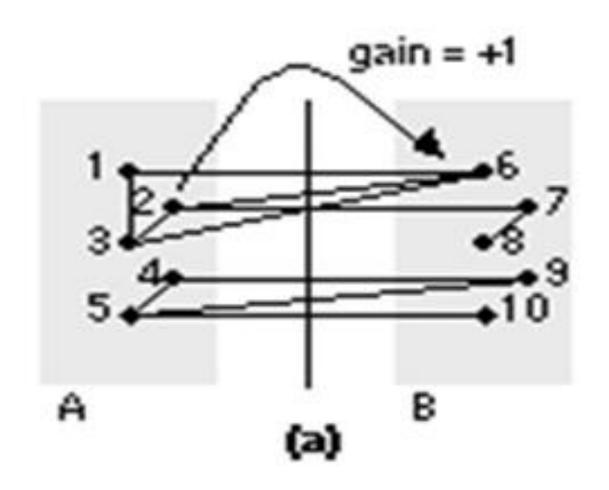

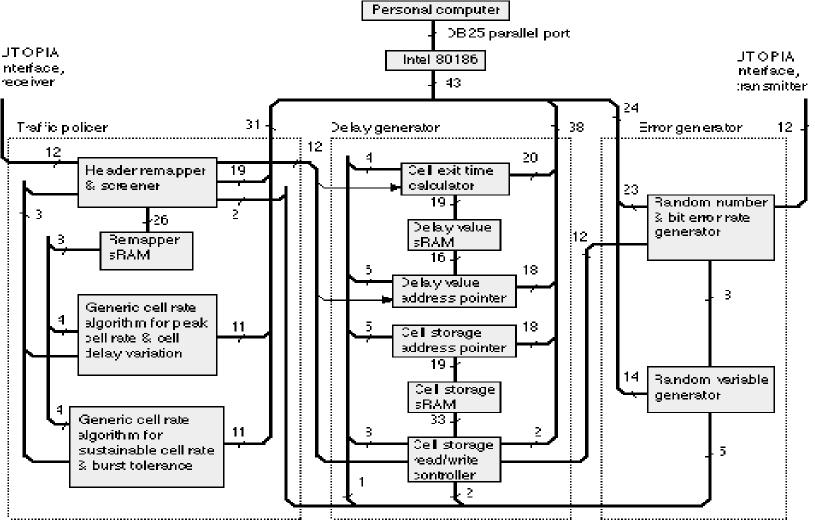

# FPGA Partitioning - An asynchronous transfer mode (ATM) connection simulator

- ATM is a signaling protocol for many different types of traffic including constant bit rates (voice signals) as well as variable bit rates (compressed video).

- The **ATM Connection Simulator is a card** that is connected to a computer.

- Under computer control the card monitors and corrupts the ATM signals to simulate the effects of real networks.

- An example would be to test different video compression algorithms.

Compressed video is very bursty (brief periods of very high activity), has very strict delay constraints, and is susceptible to errors.

#### •Asynchronous transfer mode (ATM) cell format

•FIGURE 15.4 The asynchronous transfer mode (ATM) cell format. The ATM protocol uses 53-byte cells or packets of information with a data payload and header information for routing and error control.

#### •An asynchronous transfer mode (ATM) connection simulator

### **FPGA** Partitioning

- The **simulator** is partitioned into the three major blocks

- ATM traffic policer which regulates the input to the simulator

- ATM cell delays generator which delays ATM cell, reorders ATM cells and inserts ATM cells with valid ATM cell headers.

- ATM cell error generator which produce bit errors and four random variables that are needed by the other two blocks.

- The **Traffic Policer** performs the following operations:

- Performs header screening and remapping.

- Checks ATM cell Conformance.

- Delete selected ATM Cells.

- The **delay generator** delays, misinserts and reorders the target ATM cells.

- The error generator performs the following operations:

- Payload bit error ratio generation: The user specifies the Bernoulli probability  $P_{BER}$  of the payload bit error ratio.

- Random variable generation for ATM cell loss, misinsertion, reordering and deletion.

### Automatic Partitioning with FPGAs

#### • Altera hardware design language (AHDL)

- To direct the partitioner to automatically partition logic into chips within the same family, using AUTO keyword,

DEVICE top\_level IS AUTO ; % the partitioner assign logic

- CLIQUE keyword to keep logic together

CLIQUE fast\_logic

BEGIN

| shift\_register : MACRO;% keep this in one device END;

### **Power Dissipation**

- Dynamic Power Dissipation

- Switching current from charging and discharging parasitic capacitance.

- Short-circuit current when both n -channel and p -channel transistors are momentarily on at the same time.

#### Static Power Dissipation

- Subthresold current

- Leakage current

# **Switching current**

- From charging and discharging of parasitic capacitance

- When the **p** -channel transistor in an inverter is charging a capacitance, *C*, *at a* frequency, *f*,

- the current through the transistor is I=C (d V /d t).

- The power dissipation is P=VI=CV (dV/dt) for one-half the period of the input, t = 1/(2f).

- *The power* dissipated in the p -channel transistor is thus

$$\int_{0}^{2f} Pdt = \int_{0}^{V_{DD}} CVdV = \frac{1}{2} CV_{DD}^{2}$$

- When the **n** -channel transistor discharges the capacitor, the power dissipation is equal.( ie.,  $\frac{1}{2}CV_{DD}^2$ )

- Then **total power dissipation**,  $P_1 = fCV_{DD}^2$

- **Most of the power dissipation in a CMOS ASIC** arises from this source—the switching current.

- The best way to reduce power is to reduce  $V_{DD}$  and to reduce C, the amount of capacitance we have to switch.

## **Short circuit current**

- Both n-channel and p-channel transistors momentarily on at the same time

- The **short-circuit current or crowbar current** can be particularly important for **output drivers and large clock buffers**.

- For a CMOS inverter, the **power dissipation** due to the crowbar current is

$$P_2 = \frac{\beta f t_{rf}}{12} \left( V_{DD} - 2V_{tn} \right)^3 \text{, Transistor gain factor} \beta = \frac{I_{DS}}{\left[ \left( V_{GS} - V_{tn} \right) - \frac{1}{2} V_{DS} \right] V_{DS}}$$

- Where  $\beta = (W/L)\mu C_{ox}$  is the same for both p and n -channel transistors.

- The **threshold voltages V**<sub>tn</sub> are assumed equal for both transistor types.

- *t<sub>rf</sub> is the rise and fall time* (assumed equal) of the input signal [ Veendrick, 1984].

### **Problem on Power Dissipation**

- consider an output buffer that is capable of sinking 12mA at an output voltage of 0.5 V., Derive the transistor gain factor (Assume  $V_{GS}=V_{DD}=3.3V$ ;  $V_{th}=0.65V$ )

- If the output buffer is switching at 100 MHz and the input rise time to the buffer is 2ns, Calculate the power dissipation due to short-circuit current.

- If the output load is 10 pF, Calculate the dissipation due to switching current.

- What do you infer from this?

- Inference:

$(\beta=0.01AV^{-1}, \text{ short-circuit current}, P_2=0.00133W \text{ or }1mW, \text{ switching}$ current, P<sub>1</sub>=0.01089W or 10mW)

- short-circuit current is typically less than 10 percent of the switching current  $\frac{1}{44}$

### **Subthreshold current**

- CMOS transistor is never completely off

- When the gate-to-source voltage,  $V_{GS}$ , of an MOS transistor is less than the threshold voltage,  $V_t$ , the transistor conducts a very small subthreshold current in the subthreshold region

$$I_{DS} = I_0 \exp\left(\frac{qV_{GS}}{nKT} - 1\right)$$

- where I<sub>0</sub> is a constant, and the constant, n, is normally between 1 and 2.

- The slope, S, of the transistor current in the subthreshold region is  $S = \frac{nkT}{q} \ln 10$

- Find the slope of transistor current S at a junction temperature, T = 125 °C (400 K) and assuming n = 1.5 ( assume q = 1.6 \* 10 <sup>-19</sup> Fm <sup>-1</sup>, k = 1.38 \* 10 <sup>-23</sup> JK <sup>-1</sup>). What do you infer from the result of slope of transistor current.

- Inference:

S = 120 mV/decade which does not scale.

The constant value of S = 120 mV/decade means it takes 120 mV to reduce the subthreshold current by a factor of 10 in any process.

### Leakage Current

- Transistor leakage is caused by the fact that a reverse-biased diode conducts a very small leakage current.

- The sources and drains of every transistor, as well as the junctions between the wells and substrate, form parasitic diodes.

- The parasitic-diode leakage currents are **strongly dependent** on the

- type and quality of the process

- temperature.

- The parasitic diodes have two components in parallel: an area diode and a perimeter diode.

- The leakage current due to perimeter diode is larger than area diode.

- **The ideal parasitic diode currents** are given by the following equation:

$$I = I_s \exp\left(\frac{qV_D}{nKT} - 1\right)$$

•146

# UNIT III

FLOORPLANNING Dr.K.Kalyani AP, ECE, TCE.

### Introduction

- The input to the floorplanning step **output of system partitioning and design entry**—a netlist.

- Netlist describing circuit blocks, the logic cells within the blocks, and their connections.

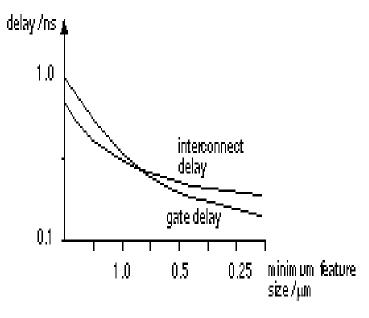

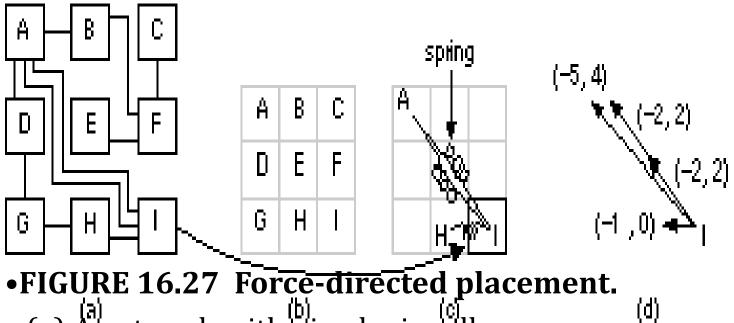

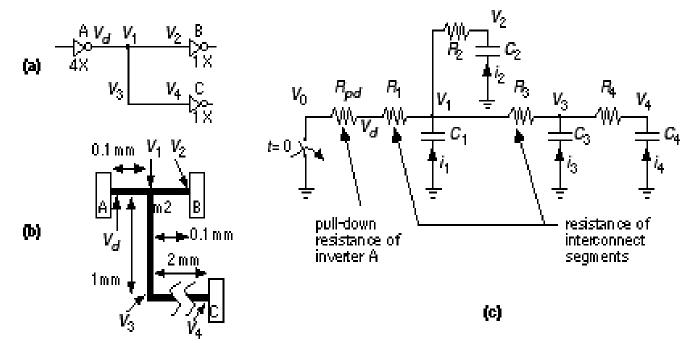

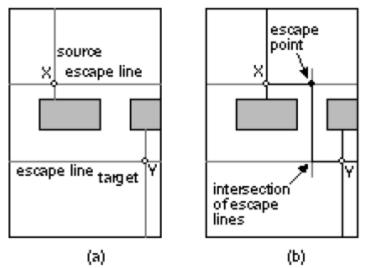

•FIGURE 16.3 Interconnect and gate delays. As feature sizes decrease, both average interconnect delay and average gate delay decrease—but at different rates. This is because interconnect capacitance tends to a limit that is independent of scaling. Interconnect delay now dominates gate delay.

•Floor planning - To predict interconnect delay by estimating interconnect length.

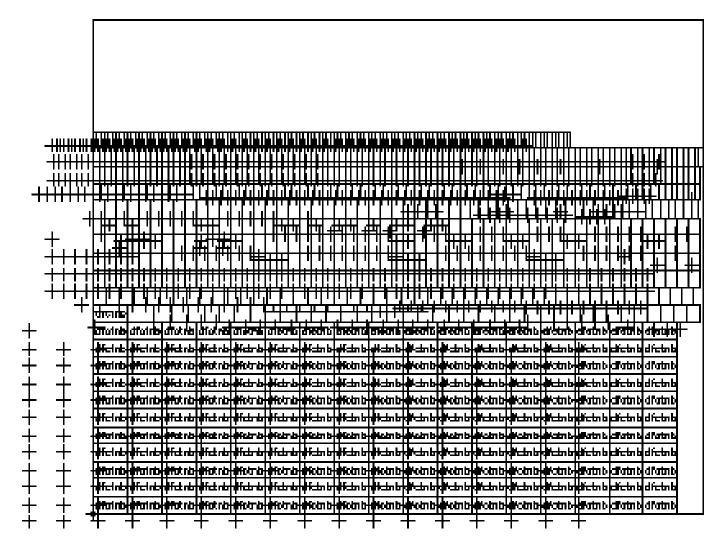

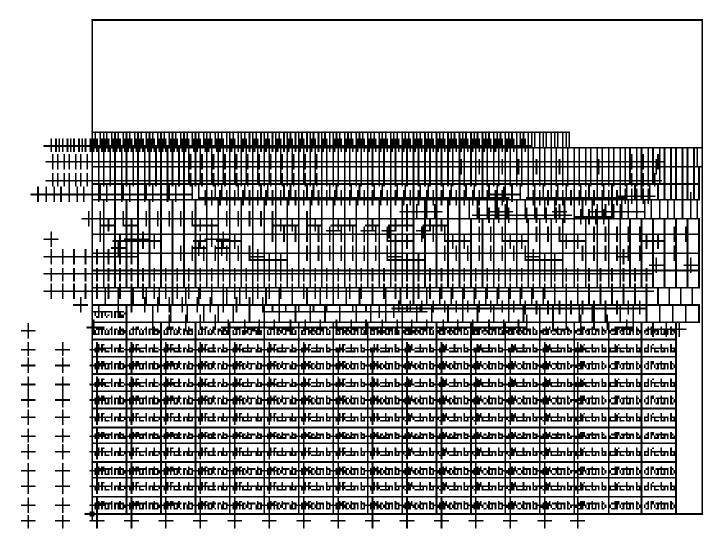

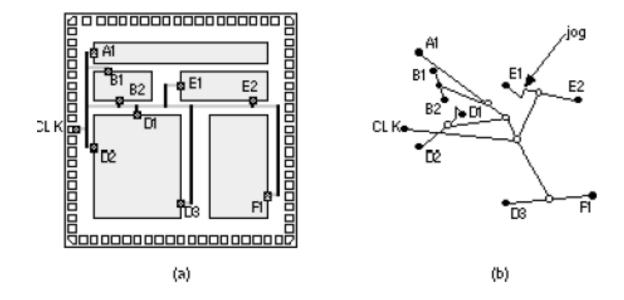

•The starting point of floorplaning and placement steps for the viterbin decoder

# •-collection of standard cells with no room set aside yet.for routing.

The starting point of floorplaning and placement steps for the viterbi decoder

- **Small boxes that look like bricks** outlines of the standard cells.

- Largest standard cells, at the bottom of the display (labeled dfctnb)

188 D flipflops.

- '+' symbols -drawing origins of the standard cells—for the D flip-flops they are shifted to the left and below the logic cell bottom left-hand corner.

- Large box surrounding all the logic cells estimated chip size.

- (This is a screen shot from Cadence Cell Ensemble.)

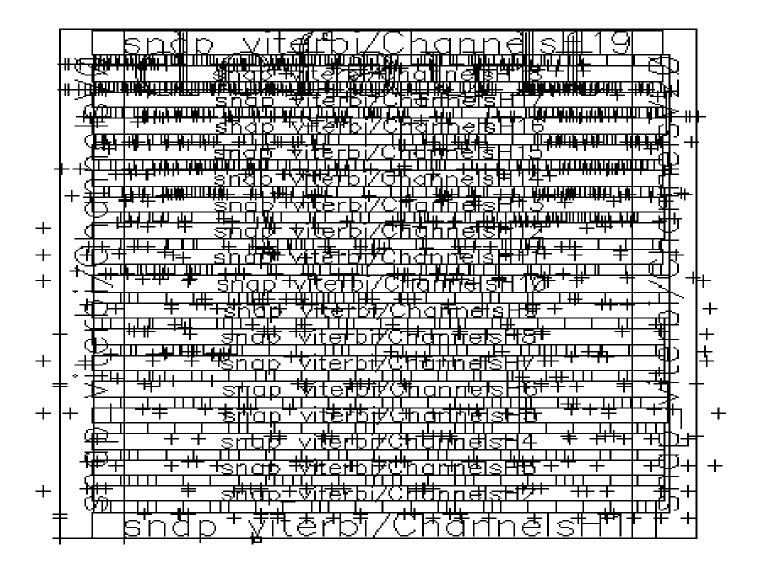

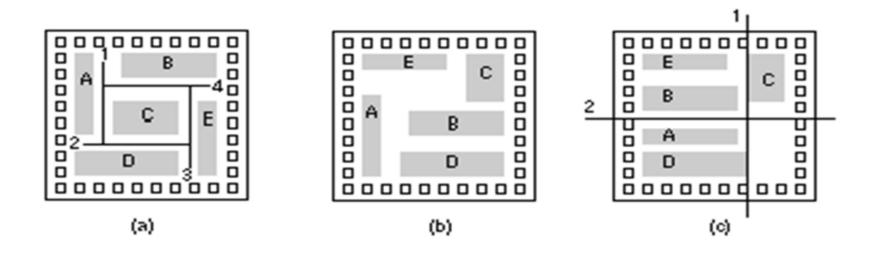

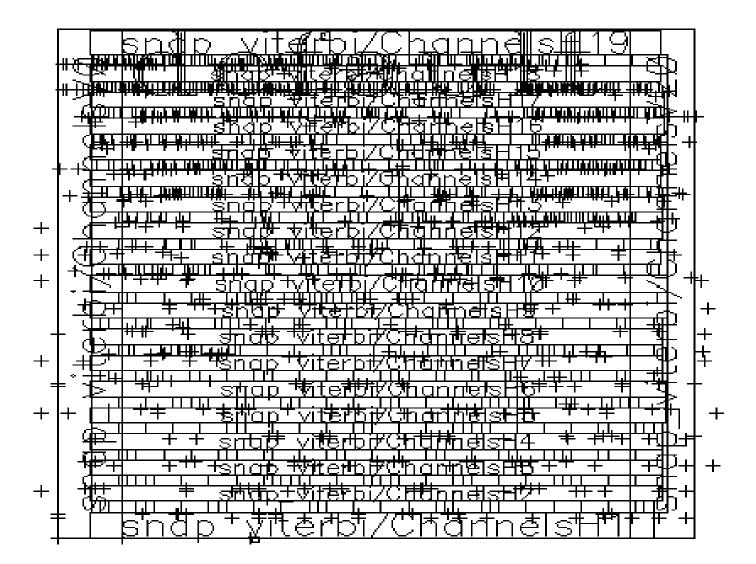

The viterbi decoder after floorplanning and placement

# The viterbi decoder after floorplanning and placement

8 rows of standard cells separated by 17 horizontal channels (labeled 2–18).

• Channels are routed as numbered.

• In this example, the I/O pads are omitted to show the cell placement more clearly.

### **Floorplanning Goals and Objectives**

- The input to a floorplanning tool is a hierarchical **netlist** that describes

- the interconnection of the blocks (RAM, ROM, ALU, cache controller, and so on)

- the logic cells (NAND, NOR, D flip-flop, and so on) within the blocks

- the logic cell connectors (terminals , pins , or ports)

- The netlist is a **logical description** of the ASIC;

- The floorplan is a physical **description** of an ASIC.

- Floorplanning is a mapping between the logical description (the netlist) and the physical description (the floorplan).

#### The **Goals of Floorplanning** are to:

- Arrange the blocks on a chip,

- Decide the location of the I/O pads,

- Decide the location and number of the power pads,

- Decide the type of power distribution, and

- Decide the location and type of clock distribution.

#### **Objectives of Floorplanning –**

To minimize the chip area

To minimize delay.

Measuring area is straightforward, but measuring delay is more difficult<sup>153</sup>

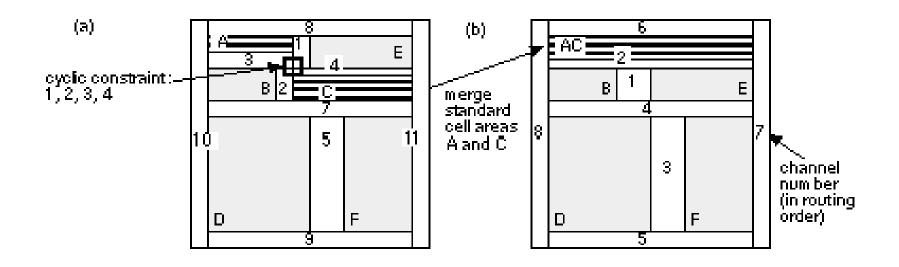

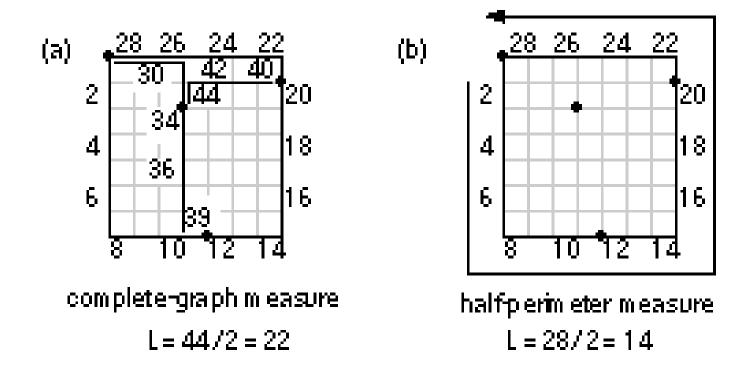

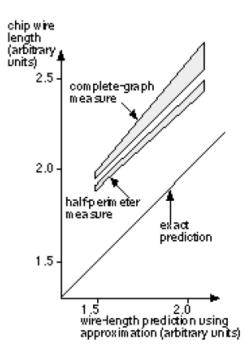

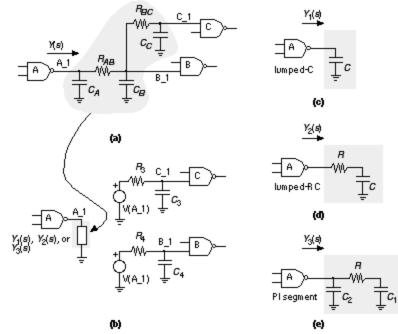

### **Measurement of Delay in Floor planning**

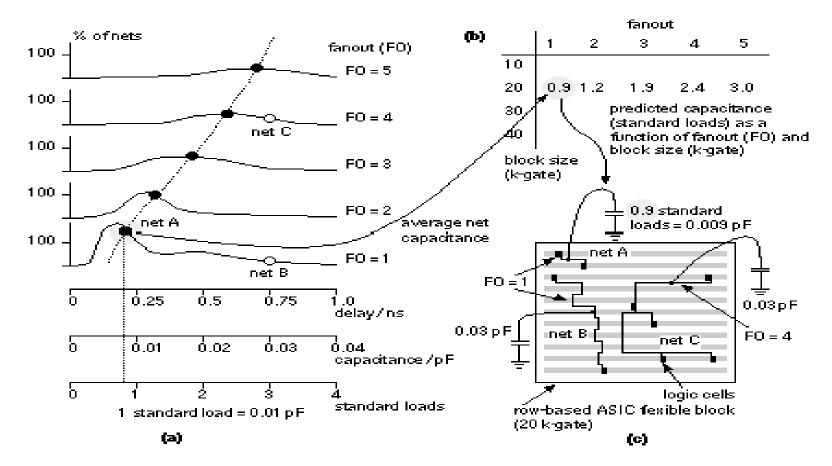

•FIGURE 16.4 Predicted capacitance. (a) Interconnect lengths as a function of fanout (FO) and circuit-block size. (b) Wire-load table. There is only one capacitance value for each fanout (typically the average value). (c) The wire-load table predicts the capacitance and delay of a net (with a considerable error). Net A and net B both have a fanout of 1, both have the same predicted net delay, but net B in fact has a much greater delay than net A in the actual layout (of course we shall not know what the actual layout is until much later in the design process).

# Measurement of Delay in Floor planning (contd.,)

- A floorplanning tool can use **predicted-capacitance tables (also known as interconnect-load tables or wire-load tables )**.

- Typically between **60 and 70 percent of nets have a F0 = 1**.

- **The distribution for a FO = 1 has a very long tail**, stretching to interconnects that run from corner to corner of the chip.

- **The distribution for a FO = 1 often has two peaks**, corresponding to